RISC-V FPGA Board Study Guide – FII-PRX100 Experimental Manuals

Version Control

| Version | Date | Descrption |

| V1.0 | 10/07/2019 | Initial Release |

| V1.1 | 16/09/2019 | Modify part of pin assignments and Ethernet description |

Contents:

Part 1 FII-PRX100 Development System Introduction 5

3. Human-computer Interaction Interface 5

4. Software Development System 6

Part 2 FII-PRX100 Main Hardware Resources Usage and FPGA Development Experiment 6

2. Create A New Project Under Vivado 6

Experiment 2 Switches and display 25

Experiment 3 Basic Digital Clock Experiment and Programming of FPGA Configuration Files 31

4.Configure the Serial Flash Programming 37

Experiment 4 Block/SCH Digital Clock Design 43

Experiment 5 Button Debounce Design and Experimental Experiment 52

Experiment 6 Digital Clock Comprehensive Design Experiment 59

3.Create an XDC File to Constrain the Clock 70

Experiment 7 Multiplier Use and ISIM Simulation 72

3.The Top-level Entity Is as Follows: 74

4.ISIM Simulation Library Compilation and Call 74

Experiment 8 Hexadecimal Number to BCD Code Conversion and Application 79

2.Application of Hexadecimal Number to BCD Number Conversion 83

Experiment 10 Use Dual_port RAM to Read and Write Frame Data 99

4.Lock the Pins, Compile, and Download to The Board to Test 107

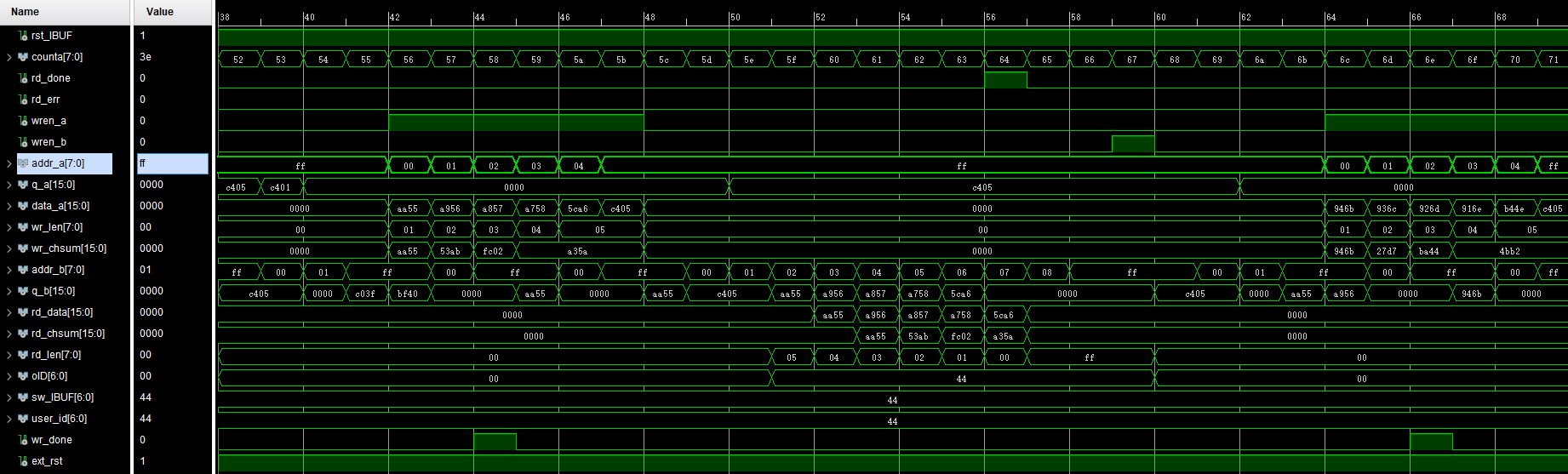

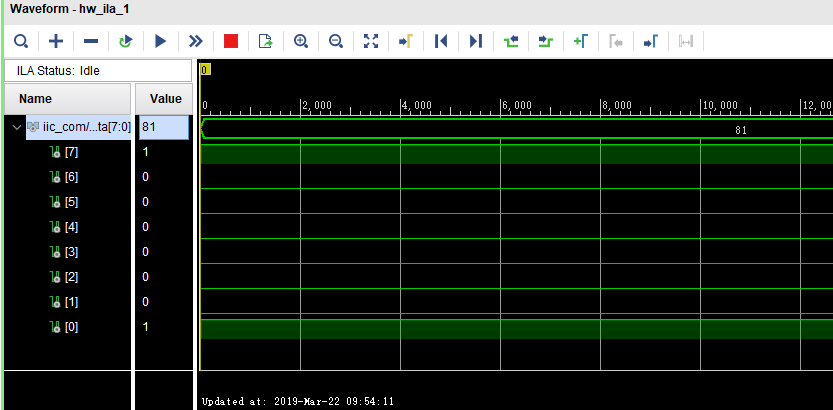

5.Use ILA to Observe Dual_port RAM Read and Write 109

6.Experiment Summary and Reflection 110

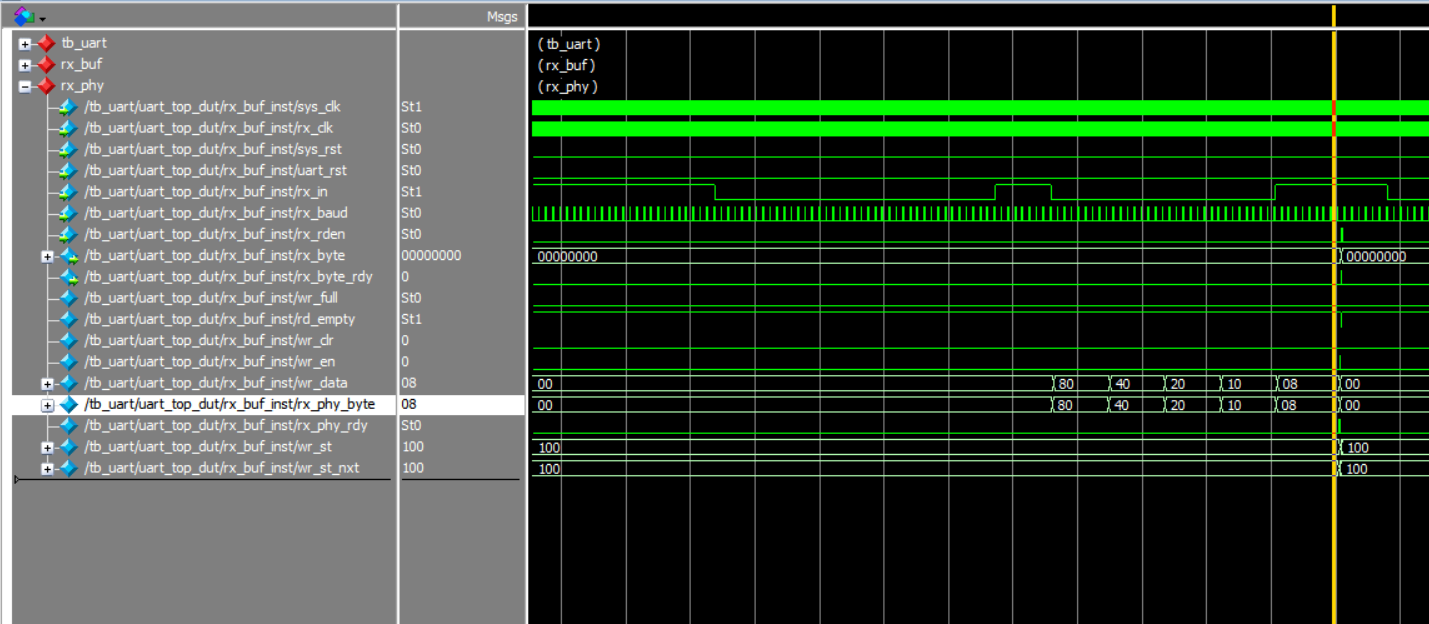

Experiment 11 Asynchronous Serial Port Design and Experiment 111

Experiment 12 IIC Protocol Transmission 143

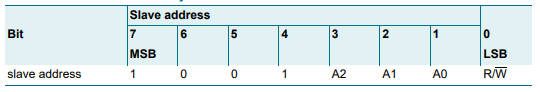

3.Introduction to the IIC Agreement 143

5.Downloading to The Board 153

Experiment 13 AD, DA Experiment 155

4.Downloading to The Board 168

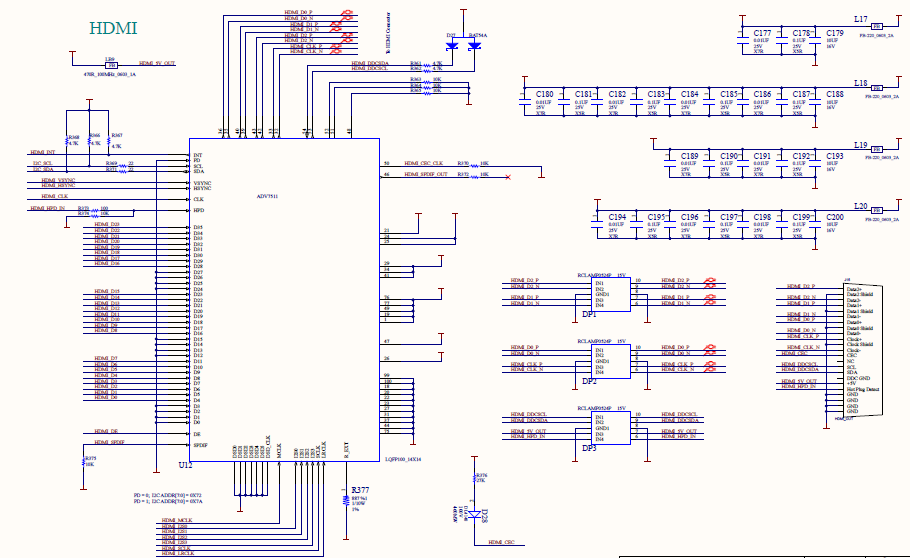

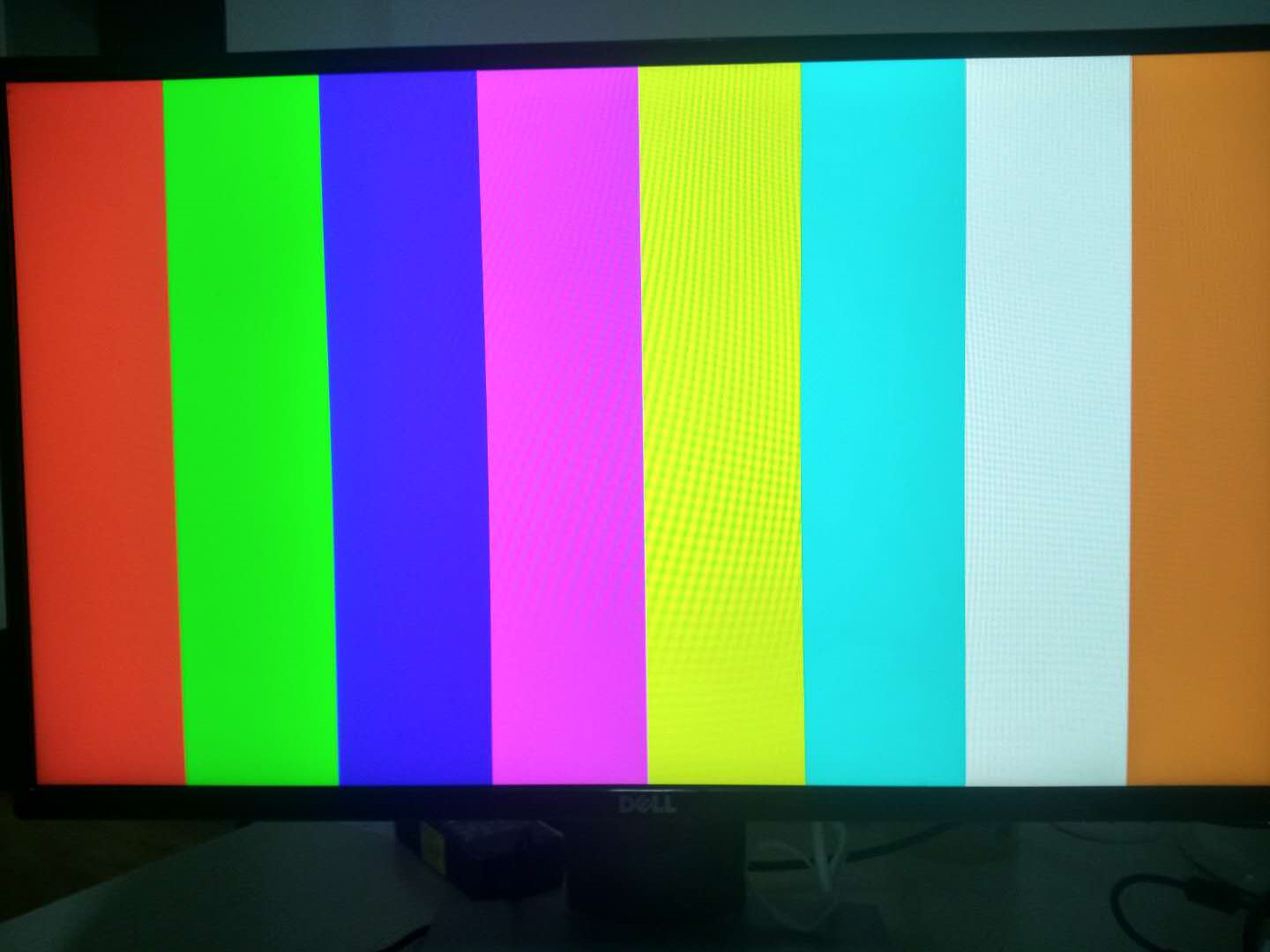

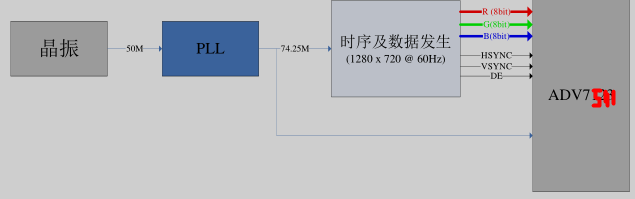

Experiment 14 HDMI Graphic Display Experiment 170

4.Download the Program to the Board to Test 178

Part 1 FII-PRX100 Development System Introduction

The main purpose of this system design is to complete FPGA learning, development and experiment with Xilin-Vivado. The main device uses the Xilinx-XC7A100T-2FGG676I and is currently the latest generation of FPGA devices from Xilinx. The main learning and development projects can be completed as follows:

- Basic FPGA design training

- Construction and training of the SOPC (Microblaze) system

- IC design and verification, the system provides hardware design, simulation and verification of RISC-V CPU

- Development and application based on RISC-V

- The system is specifically optimized for hardware design for RISC-V system applications

- System Resource

- Extended memory

- Use two Super SRAMs in parallel to form a 32-bit data interface with a maximum access space of 1M bytes.

- IS61WV25616 (2 pieces) 256K x 16bit

- Serial flash

- Spi interface serial flash (128M bytes)

- Serial EEPROM

- Gigabit Ethernet: 100/1000 Mbps

- USB to serial interface: USB-UART bridge

- Human-computer Interaction Interface

- 8 toggle switches

- 8 push buttons

- Definition of 7 push buttons: up, down, left, right, ok, menu, return

- 1 for reset: Reset button

- 8 LEDs

- 6 7-segment decoders

- I2C bus interface

- UART external interface

- Two JTAG programming interfaces: One is for downloading the FPGA debug interface, and the other one is the JTAG debug interface for the RISC-V CPU

- Built-in RISC-V CPU software debugger, no external RISC-V JTAG emulator required

- 4 12-pin GPIO connectors, in line with PMOD interface standards

- Software Development System

- Vivado 18.1 and later version for FPGA development, Microblaze SOPC

- Freedom Studio-Win_x86_64 Software development for RISC-V CPU

- Supporting Resources

RISC-V JTAG Debugger

xilinx Altera JTAG Download Debugger

FII-PRX100 Development Guide

Part 2 FII-PRX100 Main Hardware Resources Usage and FPGA Development Experiment

This part mainly guides the user to learn the development of FPGA program and the use of onboard hardware through the development example of FPGA. At the same time, the application system software Xilinx is introduced from the elementary to the profound. The development exercises covered in this section are as follows:

Experiment 1 LED Shifting

- Practice how to use the development system software Vivado to establish a new project, call the system resource PLL to establish the clock.

- Write Verilog HDL program to achieve frequency division

- Write Verilog HDL program to implement LED shifting

- Combine hardware resources for FPGA pin configuration

- Compile

- Download the program to the develop board

- Observe the experimental result and debug the project

2. Create A New Project Under Vivado

- Start Vivado in the start Menu. See Fig 1. 1

Fig 1. 1 Start Menu

Fig 1. 2 Initial interface of Vivado

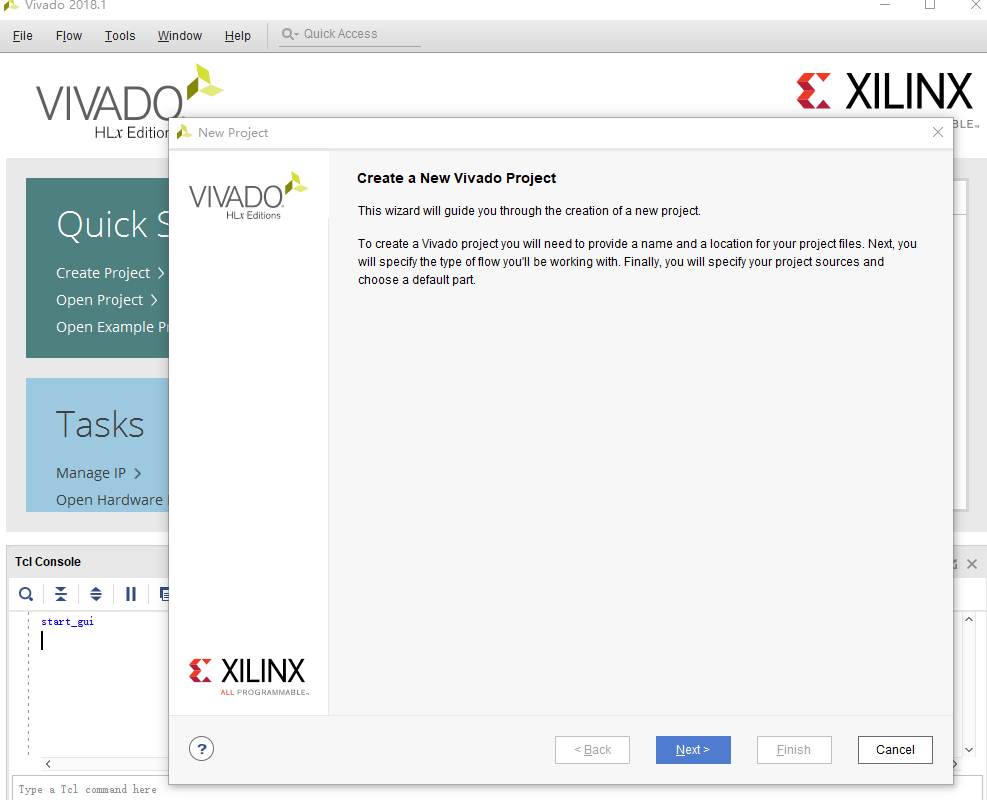

- File -> Project -> NEW

- Click the Next option button in the pop-up dialog box. Then pop up the setup project interface of Fig 1. 3 and Fig 1. 4

Fig 1. 3 Create a new project

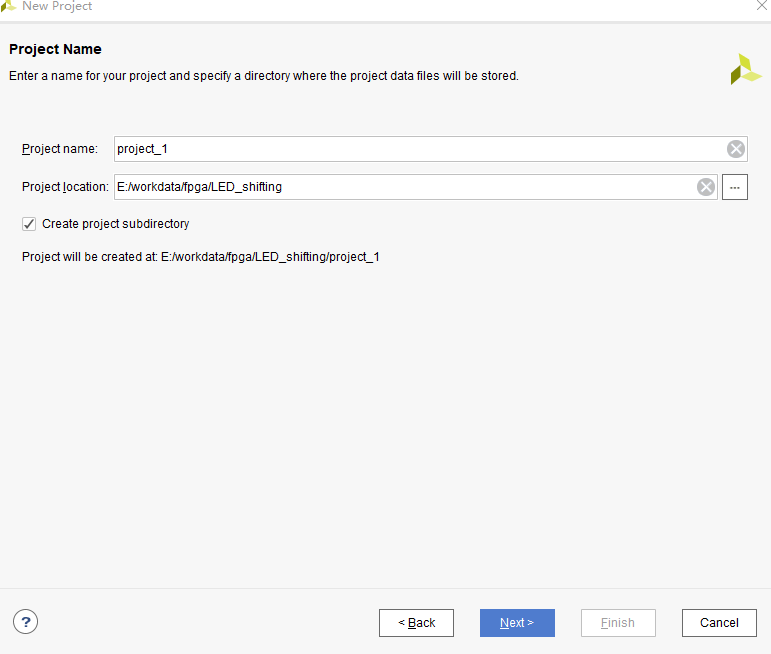

Fig 1. 4 Set the project path

Set the project name, project path. Note that the top-level file name must be consistent with the file name of the subsequent top-level file of Verilog. The top-level file name is case-sensitive.

-

- Choose RTL Project to be the project type. See Fig 1. 5.

Fig 1. 5 Project type selecting

-

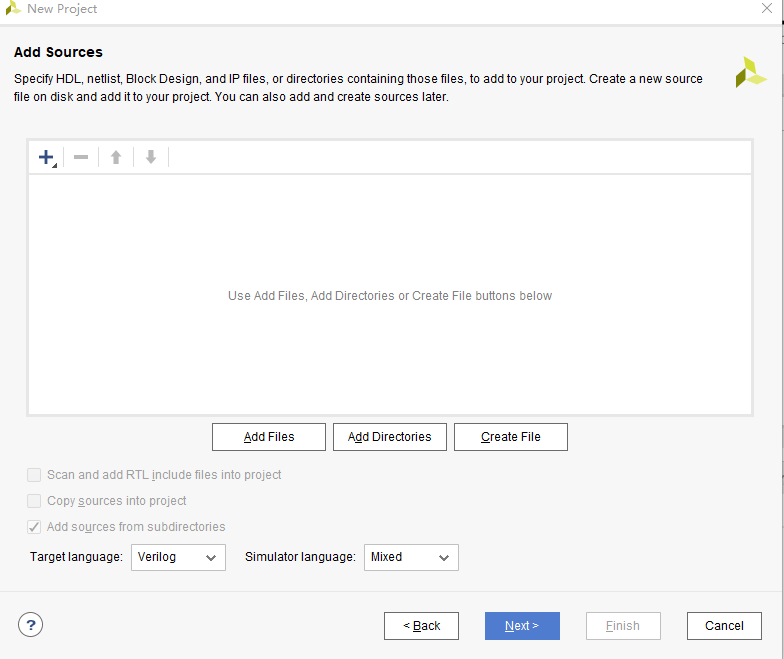

- Click Next as shown in Fig 1. 6 (there is no source file that can be added since it is new)

Fig 1. 6 Add source file

-

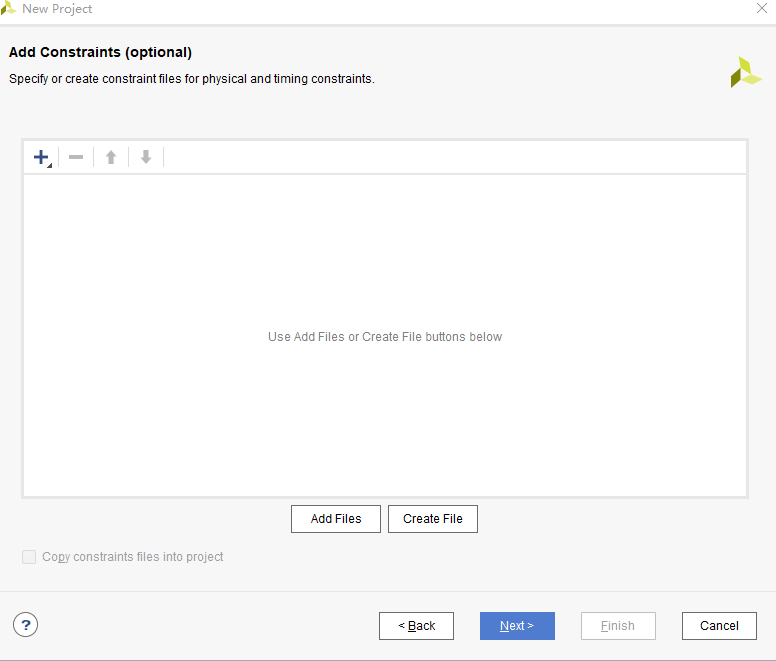

- Click Next as shown in Fig 1. 7 (there are no files that can be added to constrain due to it is a new project)

Fig 1. 7 Add constrains

-

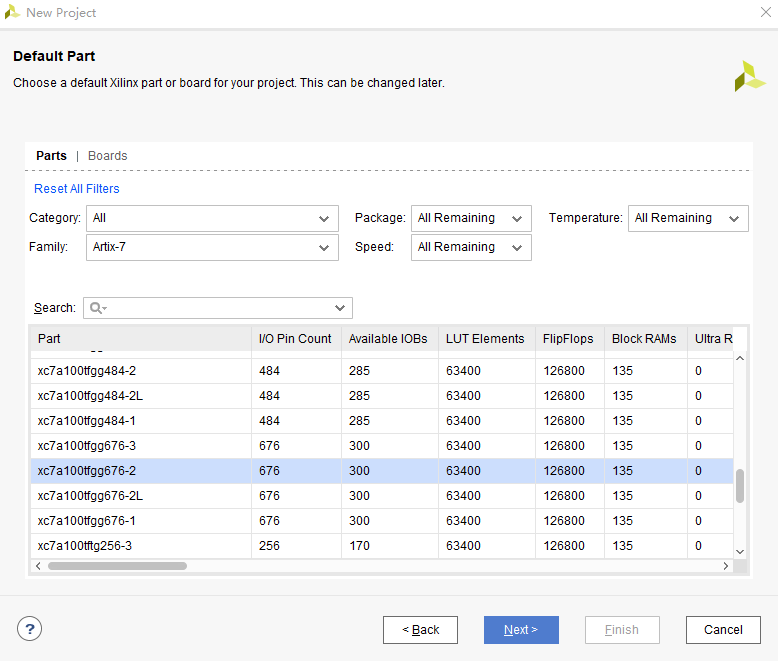

- Select XC7A100TFGG676-2 in the selection dialog box. See Fig 1. 8, click NEXT, then Finish to complete the project building.

Fig 1. 8 Choose the default Xilinx part or board

- Create a Verilog HDL file, LED_shifting.v

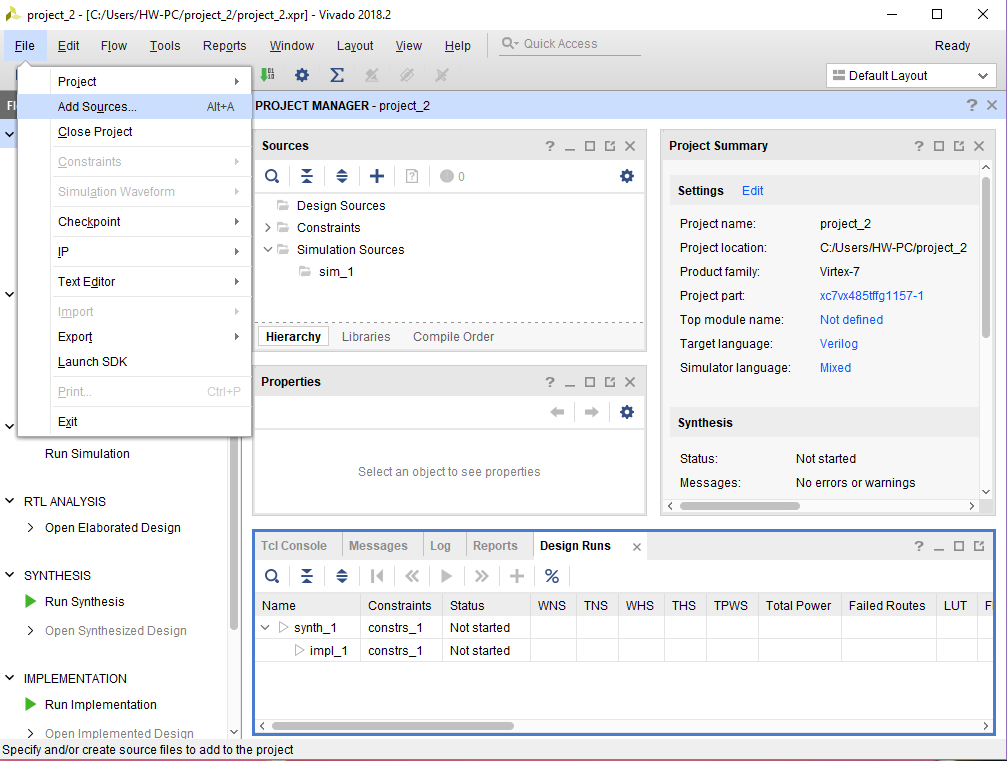

- Select File -> Add Sources or add the RTL file as shown in Fig 1. 9 or Fig 1. 10 below.

Fig 1. 9 Add source file

Fig 1. 10 Add source file

-

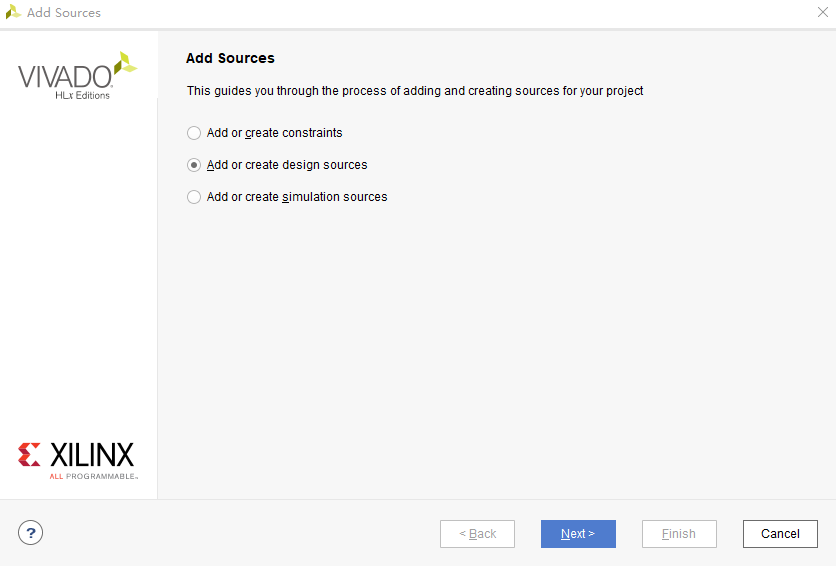

- See Fig 1. 11, select Add or create design sources and then click Next.

Fig 1. 11 Add source file 1

-

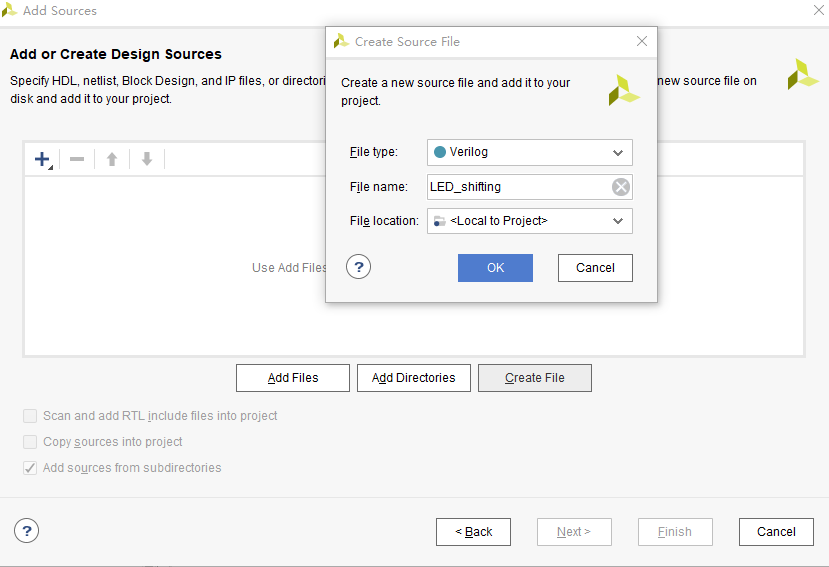

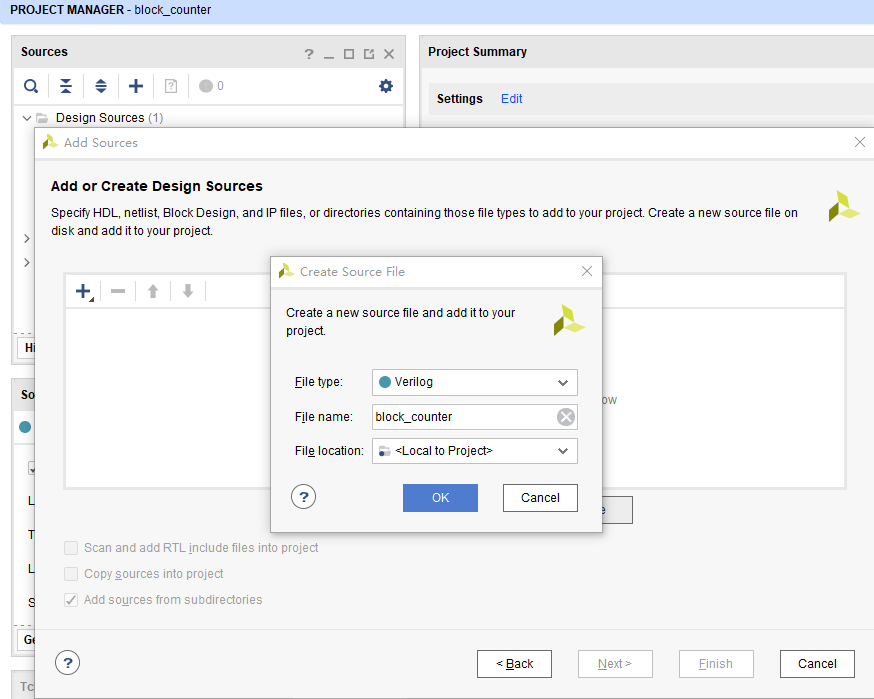

- Click Create File. In the popup window, select the Verilog HDL for the file type. Fill in the file name and location -> OK -> Finish. See Fig 1. 12.

Fig 1. 12 Add source file 2

-

- As shown in Fig 1. 13, if filling the module name wrongly in the previous step, the name can be modified here. Input and output pin configuration can also be directly set here through the I/O port definitions. (You can also write the generated pin information in the Verilog code later.) Then click OK.

Fig 1. 13 Confirmation

-

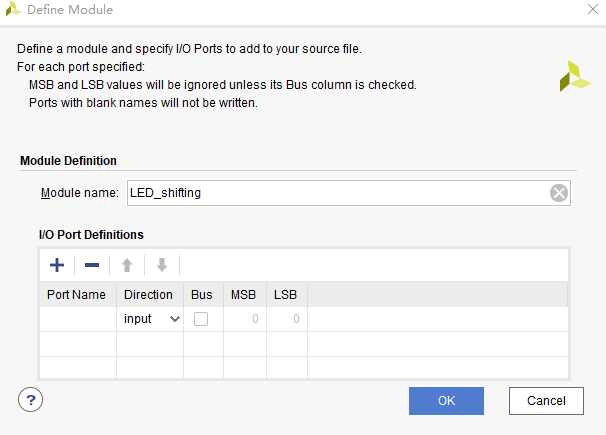

- Vivado’s sources window generates an LED_shifting RTL file. Click on the file to edit the code. See Fig 1. 14.

Code here

Fig 1. 14 Source file editing

-

- Edit interface file

module Led_shifting(

input rst,

input inclk, //c0_50Mclk

output [7:0] led

);

endmodule

- Add clock module

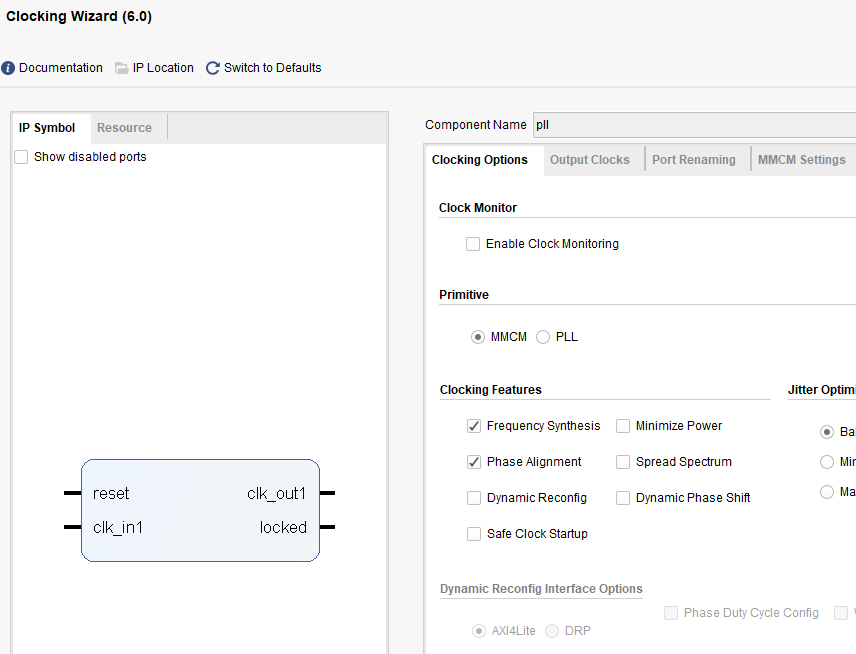

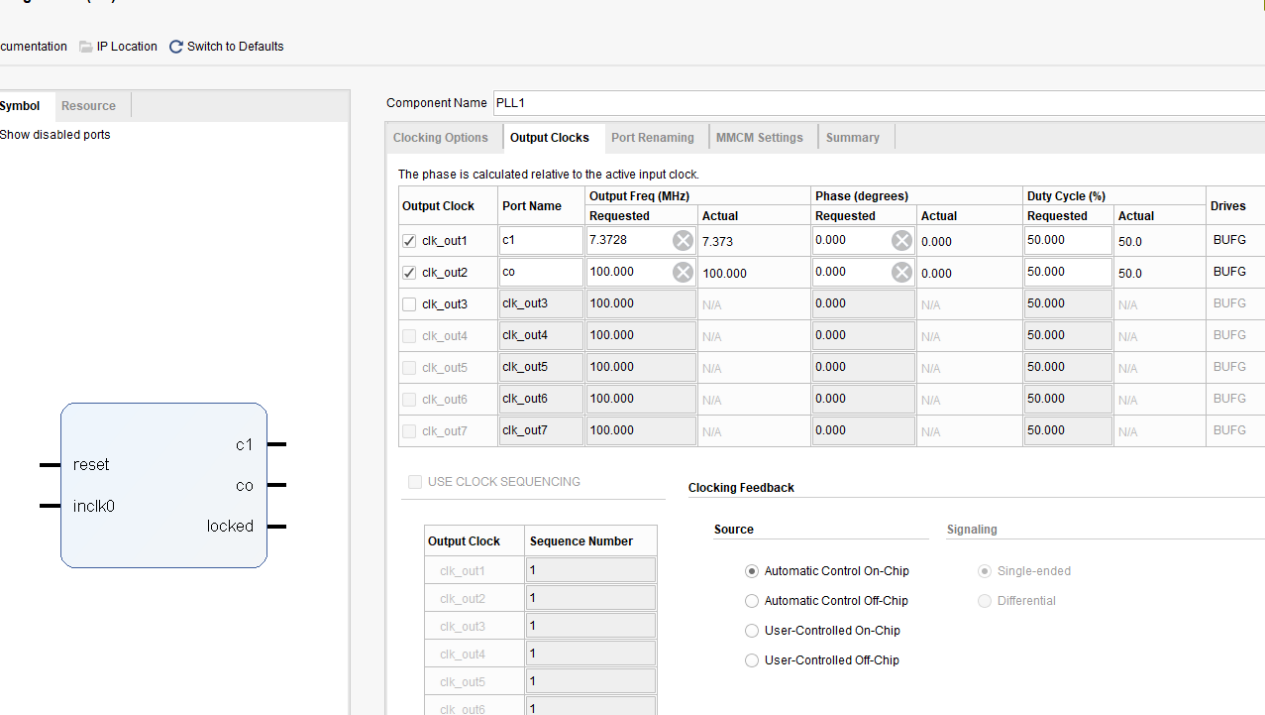

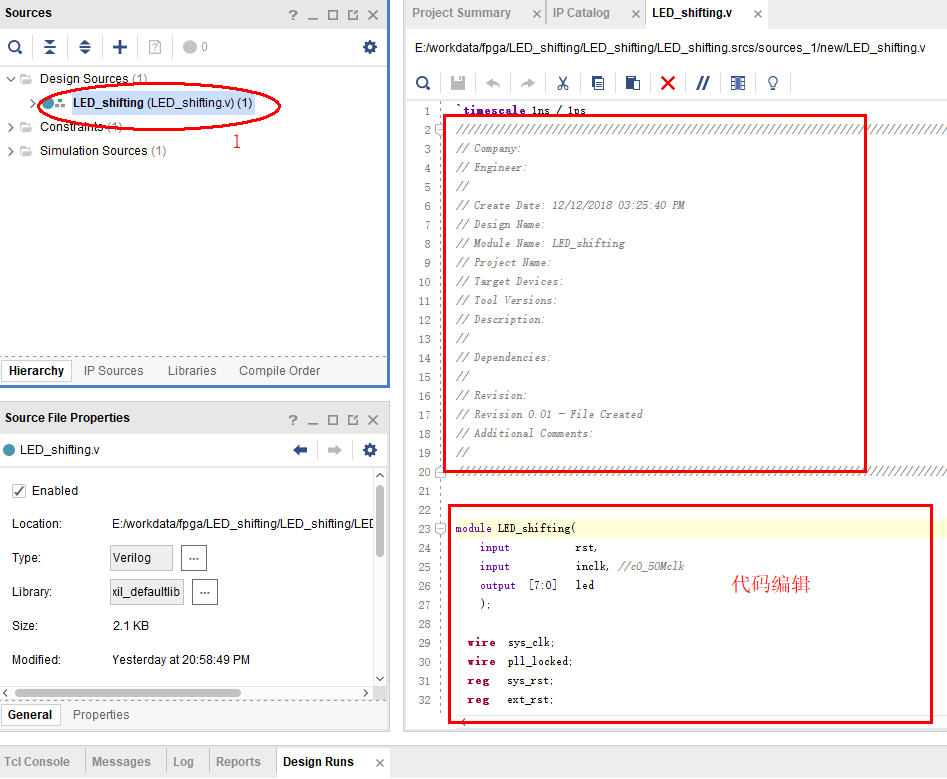

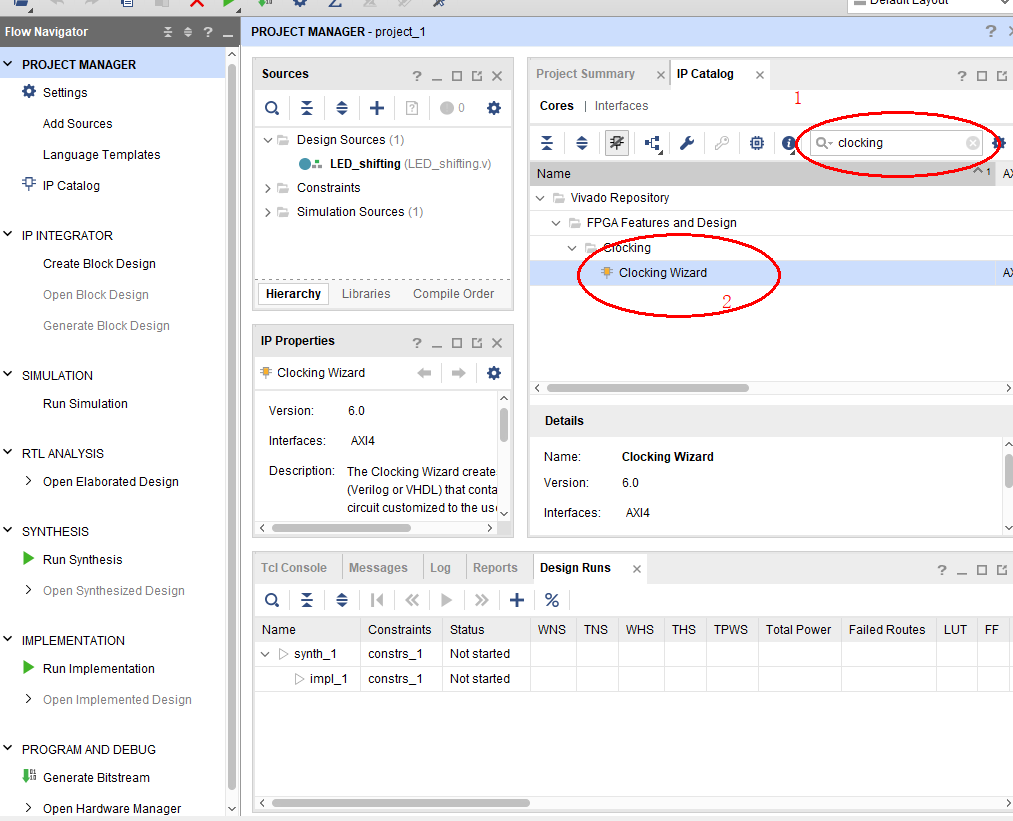

See Fig 1. 15, click the IP Catalog option on the left side of the main interface to pop up the corresponding core supported by the engineering chip. Find the needed IP core by functions or names, or by fast searching. Entering clocking in step 1, then click Clocking Wizard shown in step 2. The clock IP configuration interface will appear after that.

Fig 1. 15 PLL IP core setting

-

-

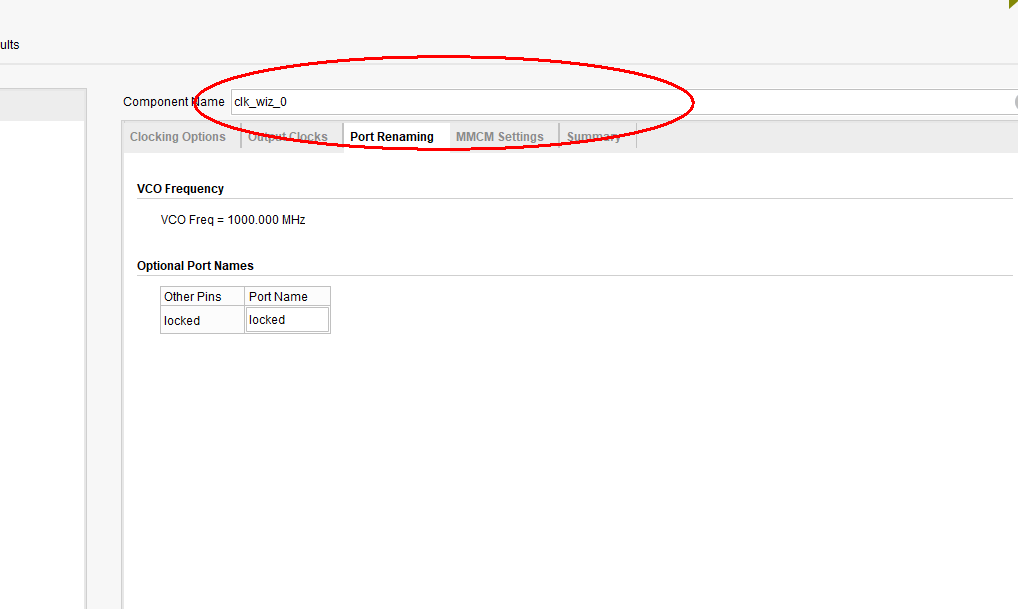

- Enter the clock setting as shown below

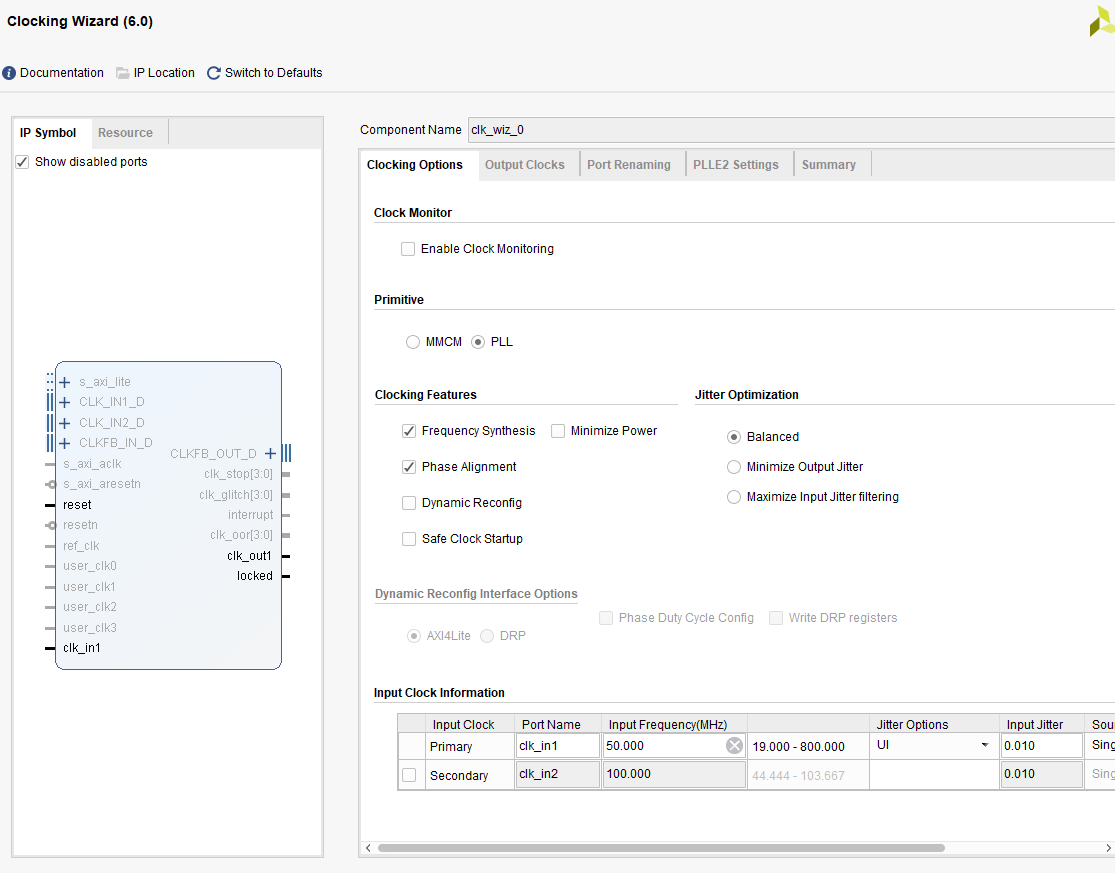

- Select either MMCM or PLL here. Here is an example of selecting a PLL core.

- The path filled in Fig 1. 16 is the setting of the clock file path. Fig 1. 17 shows the name setting.

- See Fig 1. 18, clk_in1 (which is the input clock of the PLL, where there is only one input clock) is set to be 50 MHz, which is consistent with the clock provided by the hardware board.

- Other PLL settings can be selected by default. If the required functions involve advanced features, use the official reference for more.

- Click the Output Clocks tab to set the PLL compensation output clock to clk_out1.

- For PLL asynchronous reset control and capture lock status settings, use the default mode shown in the figure.

- Enter the clock setting as shown below

-

Fig 1. 16 IP location setting window

Fig 1. 17 IP core name setting

Fig 1. 18 PLL input clock setting

-

-

-

- See Fig 1. 19, set the output frequency to 100 MHz, the phase offset to 0, and the duty cycle to 50%. Click OK.

-

-

Fig 1. 19 Output frequency and duty cycle setting

-

-

-

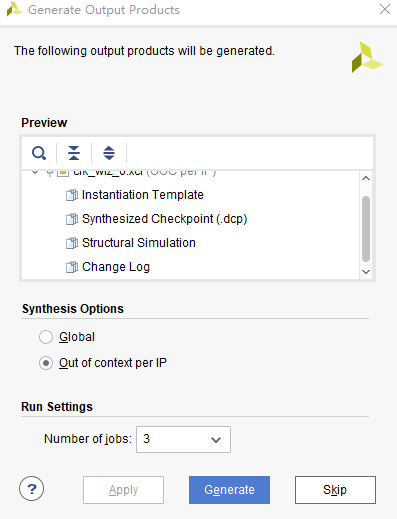

- Click Generate to finish the IP core setting. See Fig 1. 20.

-

-

Fig 1. 20 Generate IP core

-

-

-

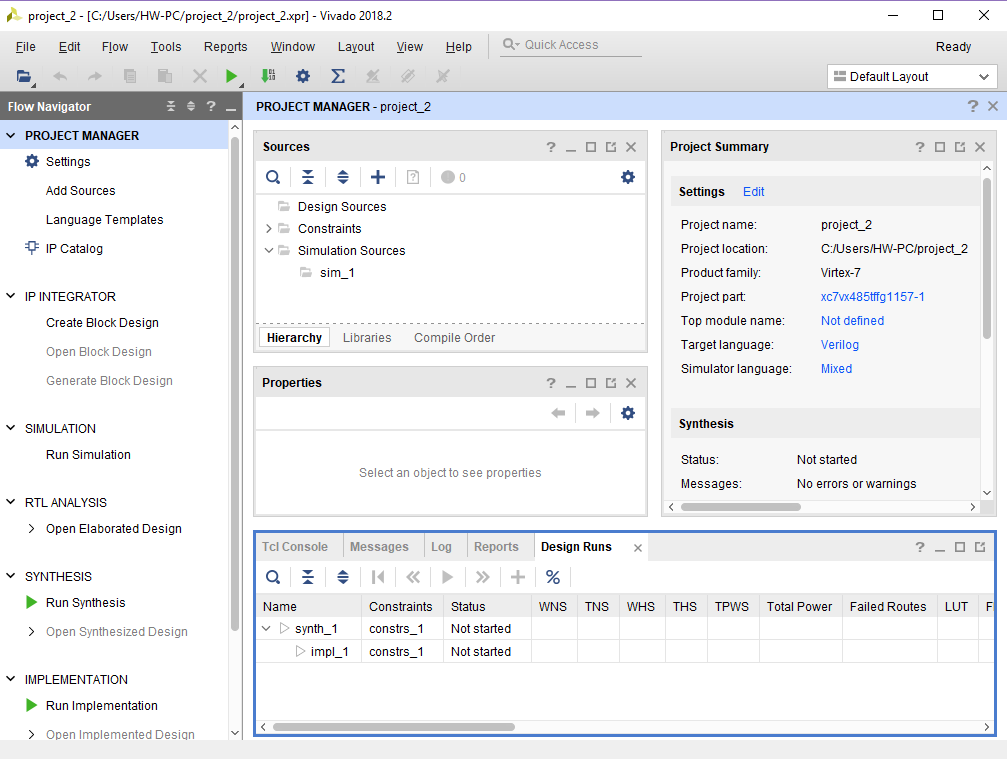

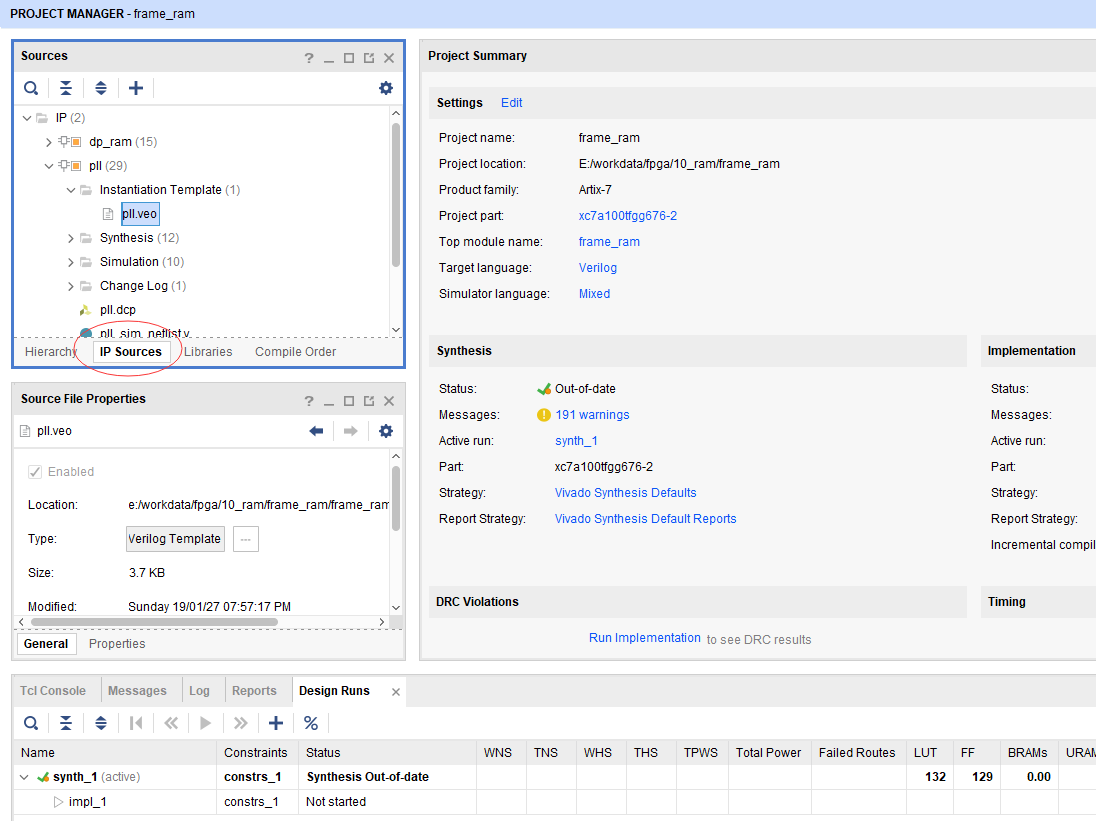

- After the clock module is generated, select the IP Sources sub-tab in the Labels box of the Sources of the project interface, that is, the IP core file can be found just after the generation. See Fig 1. 21.

- Instantiate the module to the top-level entity

-

-

Fig 1. 21 Instantiate to the top-level entity

The code is as follows:

-

-

-

- Top-level entity instance

- Key signal description

-

-

sys_rst, the value before the PLL lock is ‘1’ as a reset signal for the entire system. After the system is locked (pll_locked == 1’b1), the value of sys_rst becomes ‘0’. At the same time, it is driven by the rising edge of sys_clk, so it is a synchronous reset signal.

| module Led_shifting(

input inclk, //c0_50Mclk output [7:0] led );

wire sys_clk; wire pll_locked; reg sys_rst;

always@(posedge sys_clk) begin sys_rst<=!pll_locked; end

clk_wiz_0 clk_wiz_0_inst( .clk_out1 (sys_clk), .reset (1’b0), .locked (pll_locked), .clk_in1 (inclk) ); endmodule |

Note that the user is already familiar with the Verilog syntax by default, so the Verilog syntax is not exhaustive here.

- Frequency division design

-

- The system clock is 100 MHz, while the speed of the LED blinking is set to be 1 second, so frequency division is needed.

- Microsecond frequency division

-

The Verilog HDL code is as follows:

| reg [7:0] us_reg;

reg us_f; always@(posedge sys_clk) if(sys_rst) begin us_reg<=0; us_f<=1’b0; end else begin us_f<=1’b0; if(us_reg==99)begin us_reg<=0; us_f<=1’b1; //Microsecond pulse, outputs a sys_clk pulse every //1 us end else begin us_reg<=us_reg+1; end end |

-

-

- Millisecond frequency division

-

| reg [9:0] ms_reg;

reg ms_f; always@(posedge sys_clk) if(sys_rst) begin ms_reg<=0; ms_f<=1’b0; end else begin ms_f<=1’b0; if(us_f) begin if(ms_reg==999)begin //Every 1000 microseconds, ms_f //produces a sys_clk pulse ms_reg<=0; ms_f<=1’b1; end else//Counter adds 1 every microsecond ms_reg<=ms_reg+1; end end |

-

-

- Second frequency division

-

| always@(posedge sys_clk)

if(sys_rst) begin s_reg<=0; s_f<=1’b0; end else begin s_f<=1’b0; if(ms_f) begin if(s_reg==999)begin s_reg<=0; s_f<=1’b1; end else s_reg<=s_reg+1; end end |

-

-

- LED shifting design

-

| always@(posedge sys_clk)

if(sys_rst) begin s_reg<=0; s_f<=1’b0; end else begin s_f<=1’b0; if(ms_f) begin if(s_reg==999)begin s_reg<=0; s_f<=1’b1; end else s_reg<=s_reg+1; end end |

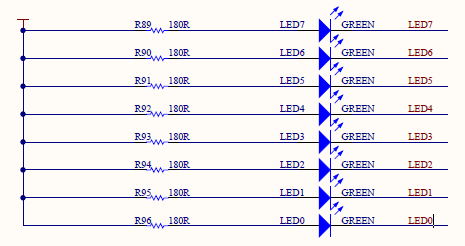

Because the schematics design uses FPGA I/O sink current mode, it must be inverted bitwise before output. Otherwise, it will show that each time 7 LEDs are lit, only one LED is left in the non-lighting state.

Assign led=~led_r; //Bitwise inverse

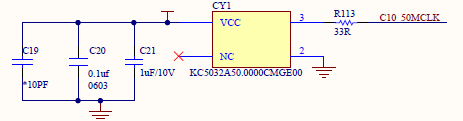

The pin assignment table of the program is as follows:

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk | System clock 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| led0 | LED 0 | LED0 | N17 |

| led1 | LED 1 | LED1 | M19 |

| led2 | LED 2 | LED2 | P16 |

| led3 | LED 3 | LED3 | N16 |

| led4 | LED 4 | LED4 | N19 |

| led5 | LED 5 | LED5 | P19 |

| led6 | LED 6 | LED6 | N24 |

| led7 | LED 7 | LED7 | N23 |

Fig 1. 22 Schematics for LED

Fig 1. 23 FPGA input clock

- After the code is integrated, there are two ways to add the constraint file. One is to use the I/O planning function in Vivado, and the other is to directly create a constraint file for the XDC and manually enter the constraint command. Here the first method is adopted for now, I/O planning function. The procedure is as follows

-

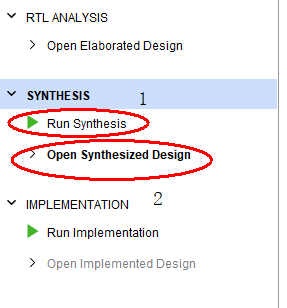

- Go to Flow Navigator -> Synthesis -> Run Synthesis, integrate the project first. See Fig 1. 24. The purpose is:

- Check the syntax error

- Form the tree hierarchy of the project

- Go to Flow Navigator -> Synthesis -> Run Synthesis, integrate the project first. See Fig 1. 24. The purpose is:

-

Fig 1. 24 Check the syntax, compilation synthesis

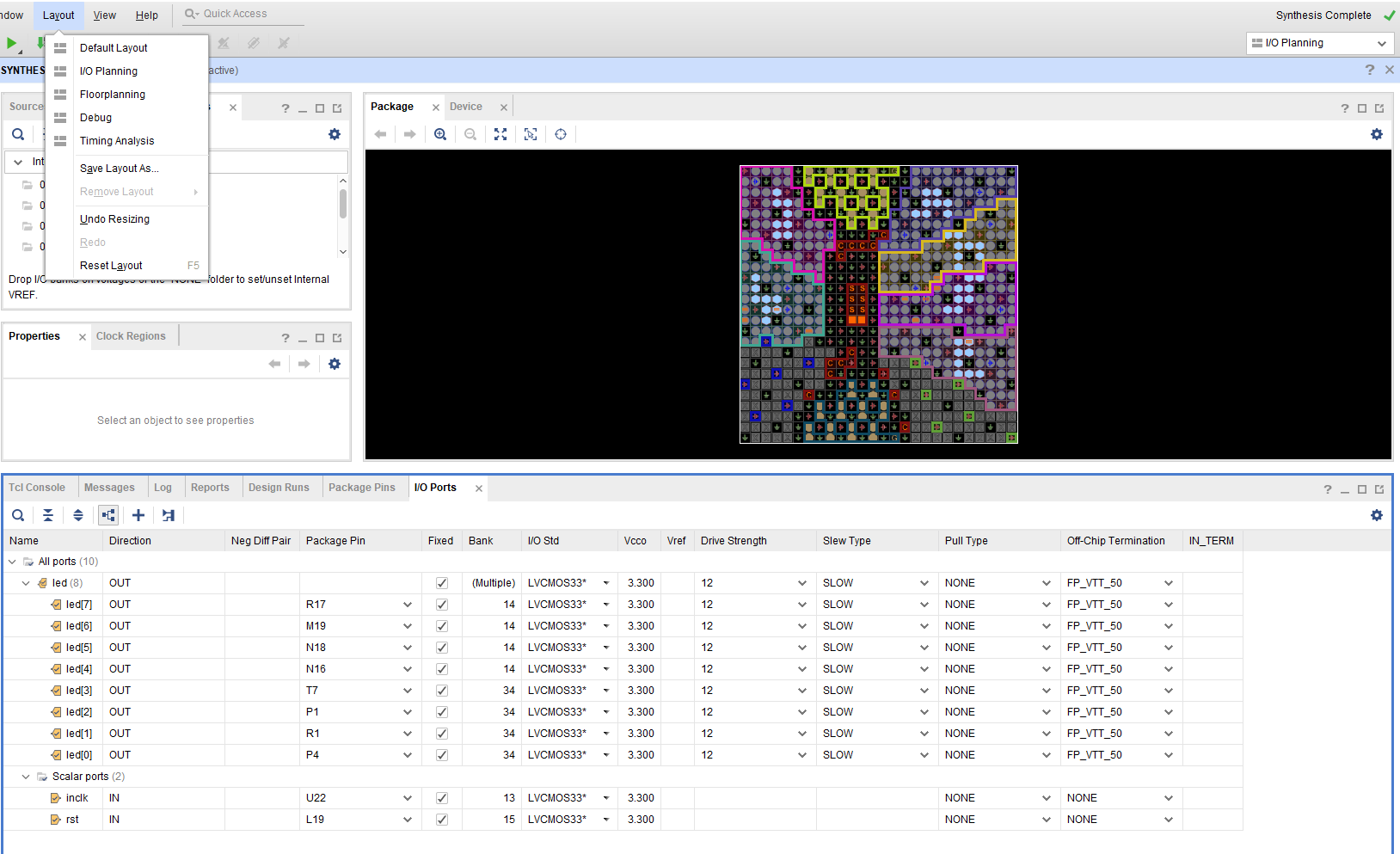

After the integration is complete, select Open Synthesized Design, open the comprehensive results, select I/O Planning under layout, and assign the pins in the I/O port section in the figure below.

Fig 1. 25 Pin assignment

-

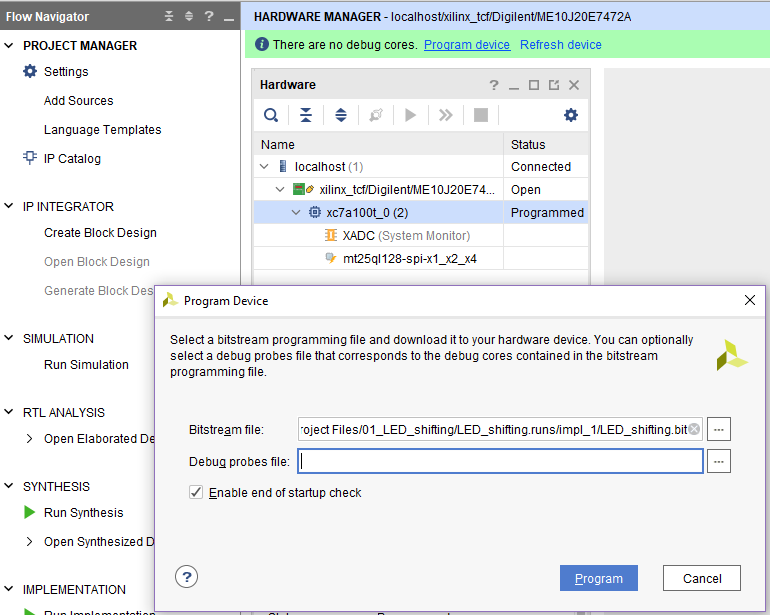

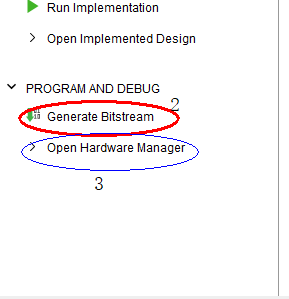

- After the pin assignment is completed, click Run Implementation as shown in Fig 1. 26. After the completion of the Generate Bitstream, generate a downloadable bit file. Click Open Hardware Manager to link to the device. See Fig 1. 27.

Fig 1. 26 Generate bit files Fig 1. 27 Connect with the experiment board

-

- As shown in Fig 1. 28 below, select the correct bit file and download the bit file settings.

Fig 1. 28 Download the bit file configuration

-

- Click Program to download the program to the board to test

-

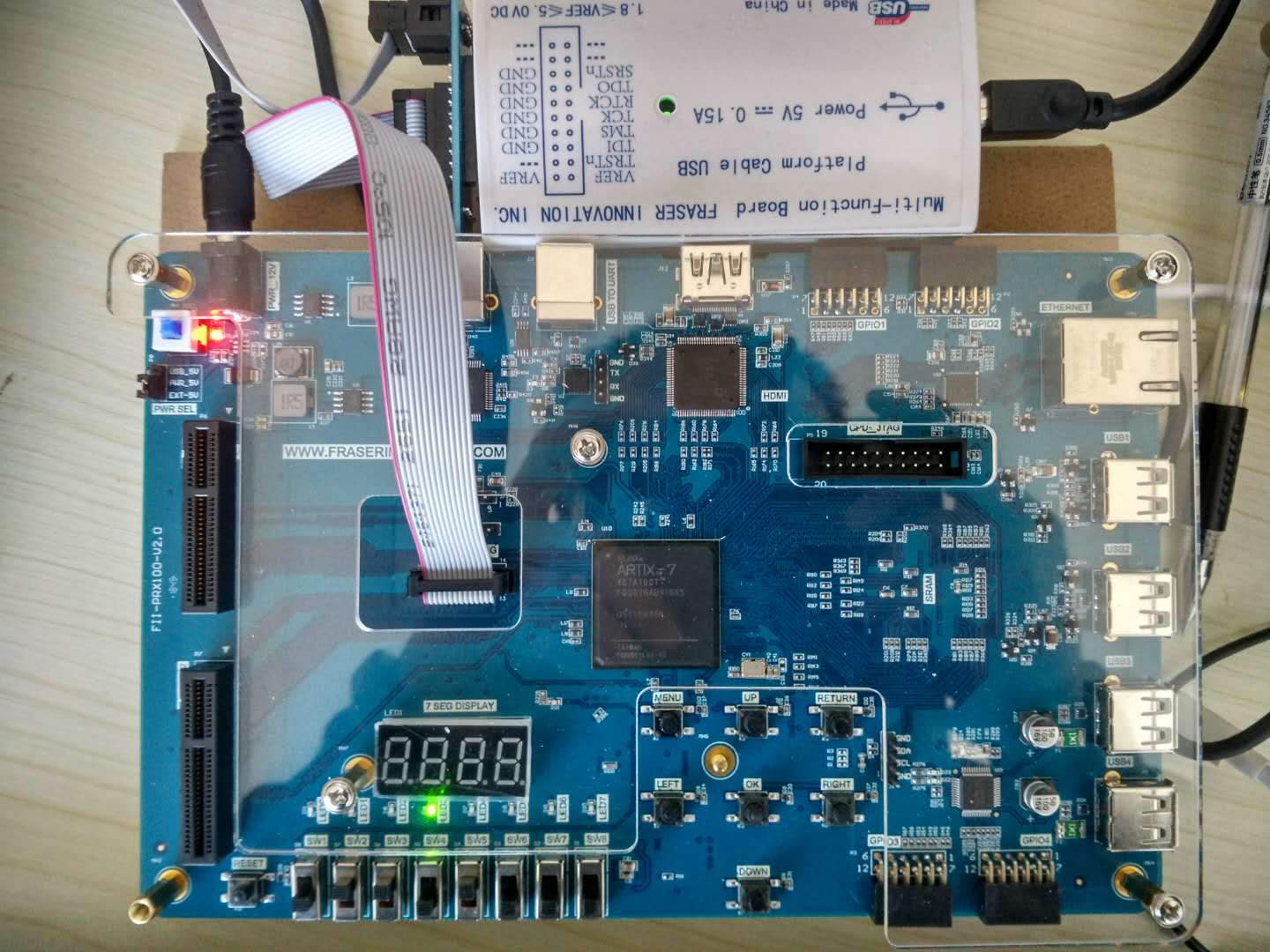

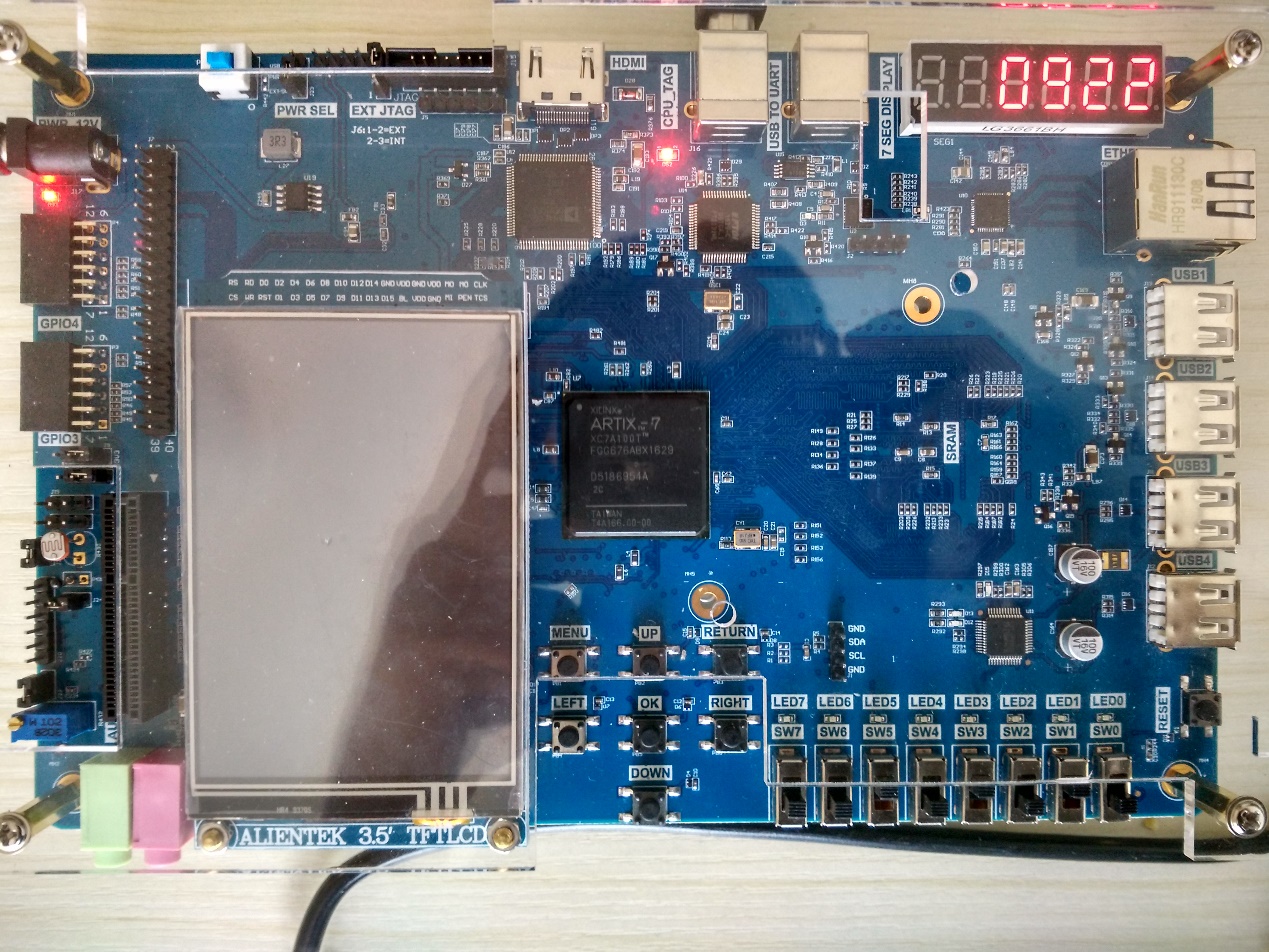

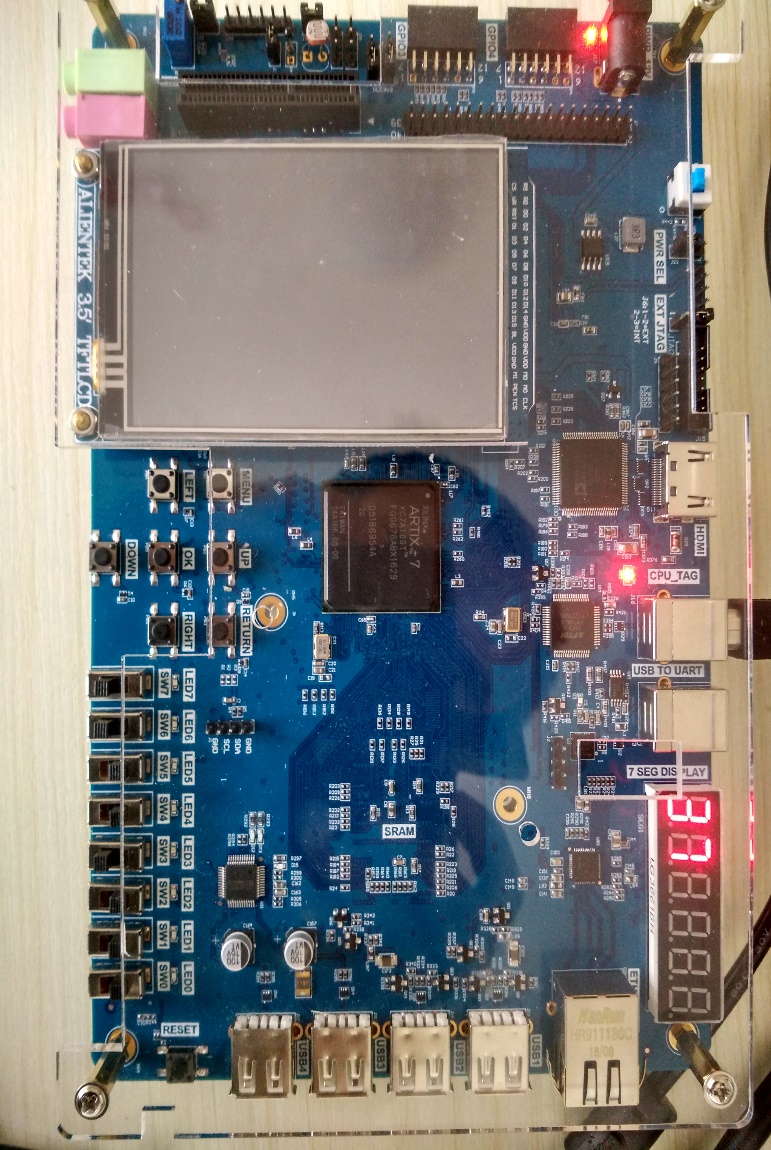

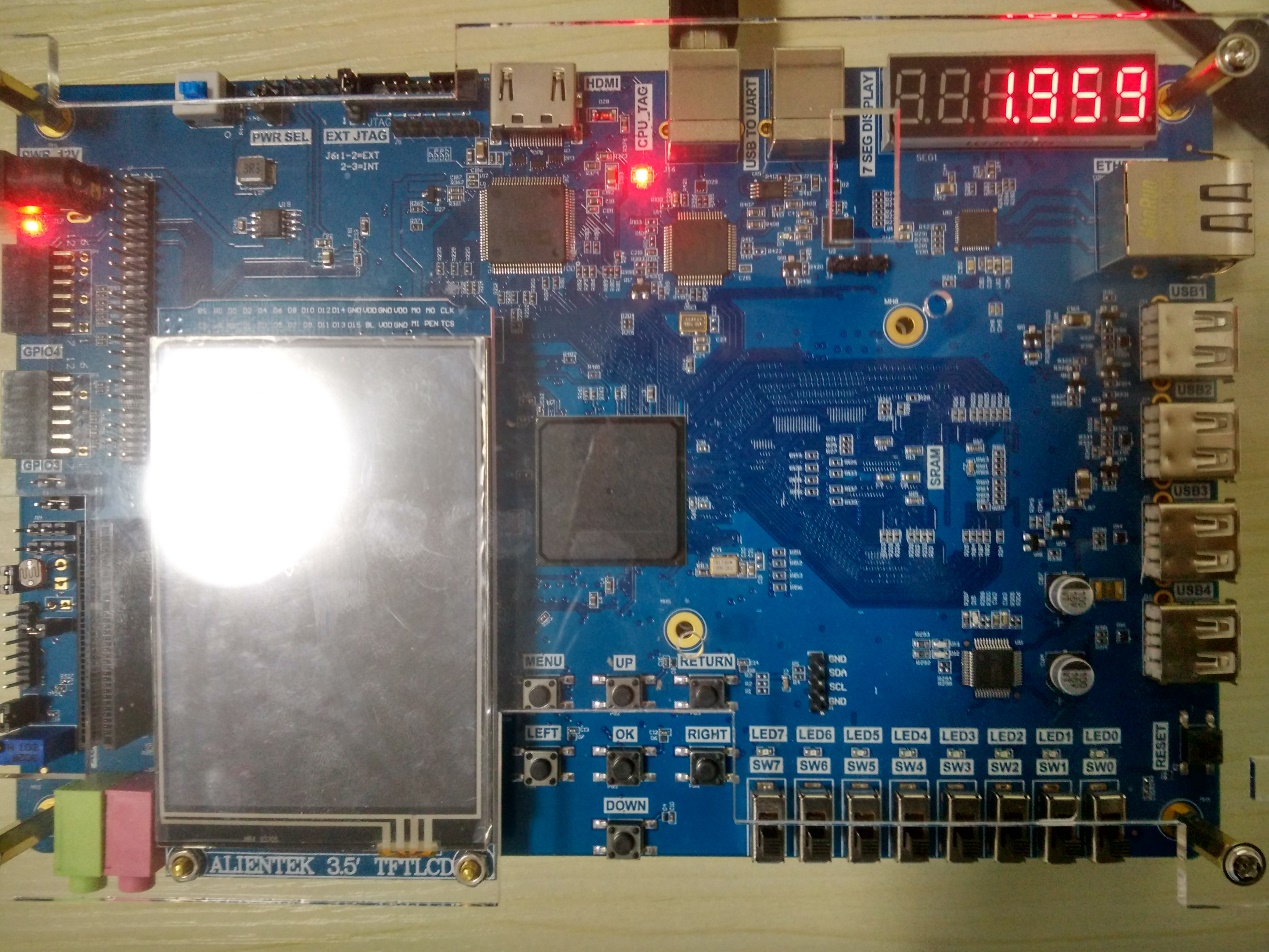

- The hardware connection is shown as follows, the 8 LEDs blink one by one.

-

- Click Program to download the program to the board to test

Fig 1. 29 Develop board

-

-

-

- Review the above steps to be proficient in each process

-

-

Experiment 2 Switches and display

1.Experiment Objective

-

- Continue to practice using develop board

- Learn to use ILA (Integrated Logic Analyzer) in Vivado

- Learn to use the FPGA configuration memory for programming

2.Start New Project

-

- Refer to Experiment 1

- Select the same chip in Experiment 1

- Add PLL1 (Here PLL1 is optional, external input clock can be used directly)

3.Verilog HDL Code

| module SW_LED(

input inclk, input [7:0] sw, output reg[7:0] led ); wire sys_clk; wire pll_locked; reg sys_rst; always@(posedge sys_clk) sys_rst<=!pll_locked;

always @(posedge inclk) if(sys_rst) led<=8’hff; else led<=~sw; PLL1 PLL1_INST( .reset (1’b0), .clk_in1 (inclk), .clk_out1 (sys_clk), .locked (pll_locked) ); endmodule |

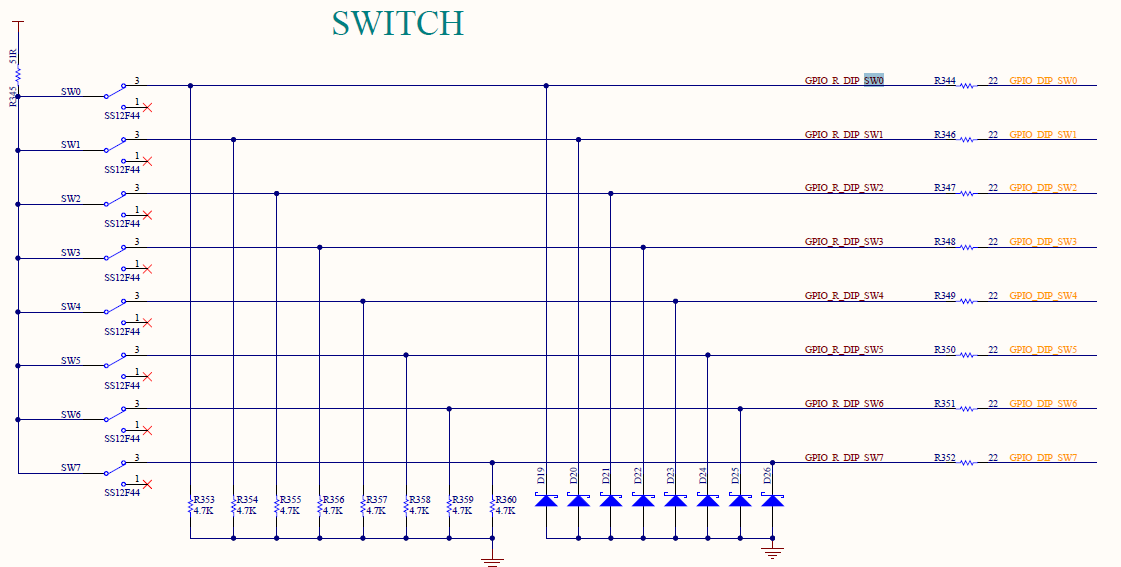

Schematics of develop board

-

- See Fig 2. 1. the diodes D19-D26 are mainly used to eliminate the damage of the FPGA pin caused by human body contact static electricity.

Fig 2. 1 Switches drive the circuit

4.FPGA Pin Assignment

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk | System Clock 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| led0 | LED 0 | LED0 | N17 |

| led1 | LED 1 | LED1 | M19 |

| led2 | LED 2 | LED2 | P16 |

| led3 | LED 3 | LED3 | N16 |

| led4 | LED 4 | LED4 | N19 |

| led5 | LED 5 | LED5 | P19 |

| led6 | LED 6 | LED6 | N24 |

| led7 | LED 7 | LED7 | N23 |

| SW0 | SW 0 | GPIO_DIP_SW0 | N8 |

| SW1 | SW 1 | GPIO_DIP_SW1 | M5 |

| SW2 | SW 2 | GPIO_DIP_SW2 | P4 |

| SW3 | SW 3 | GPIO_DIP_SW3 | N4 |

| SW4 | SW 4 | GPIO_DIP_SW4 | U6 |

| SW5 | SW 5 | GPIO_DIP_SW5 | U5 |

| SW6 | SW 6 | GPIO_DIP_SW6 | R8 |

| SW7 | SW 7 | GPIO_DIP_SW7 | P8 |

5.Program in Vivado

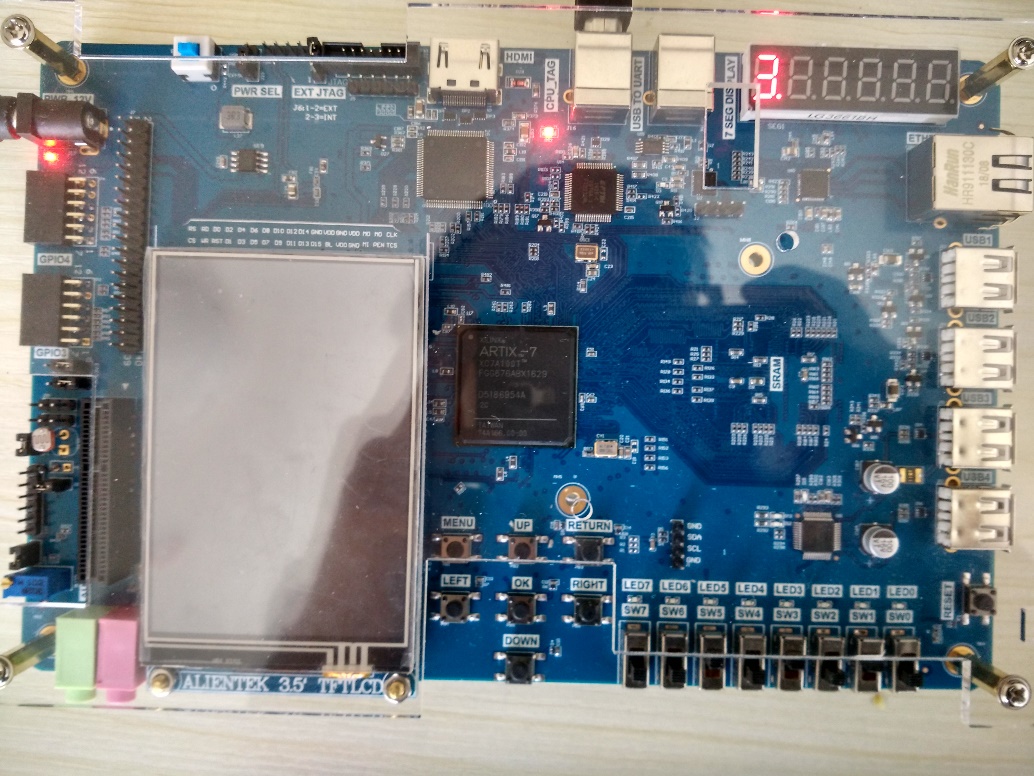

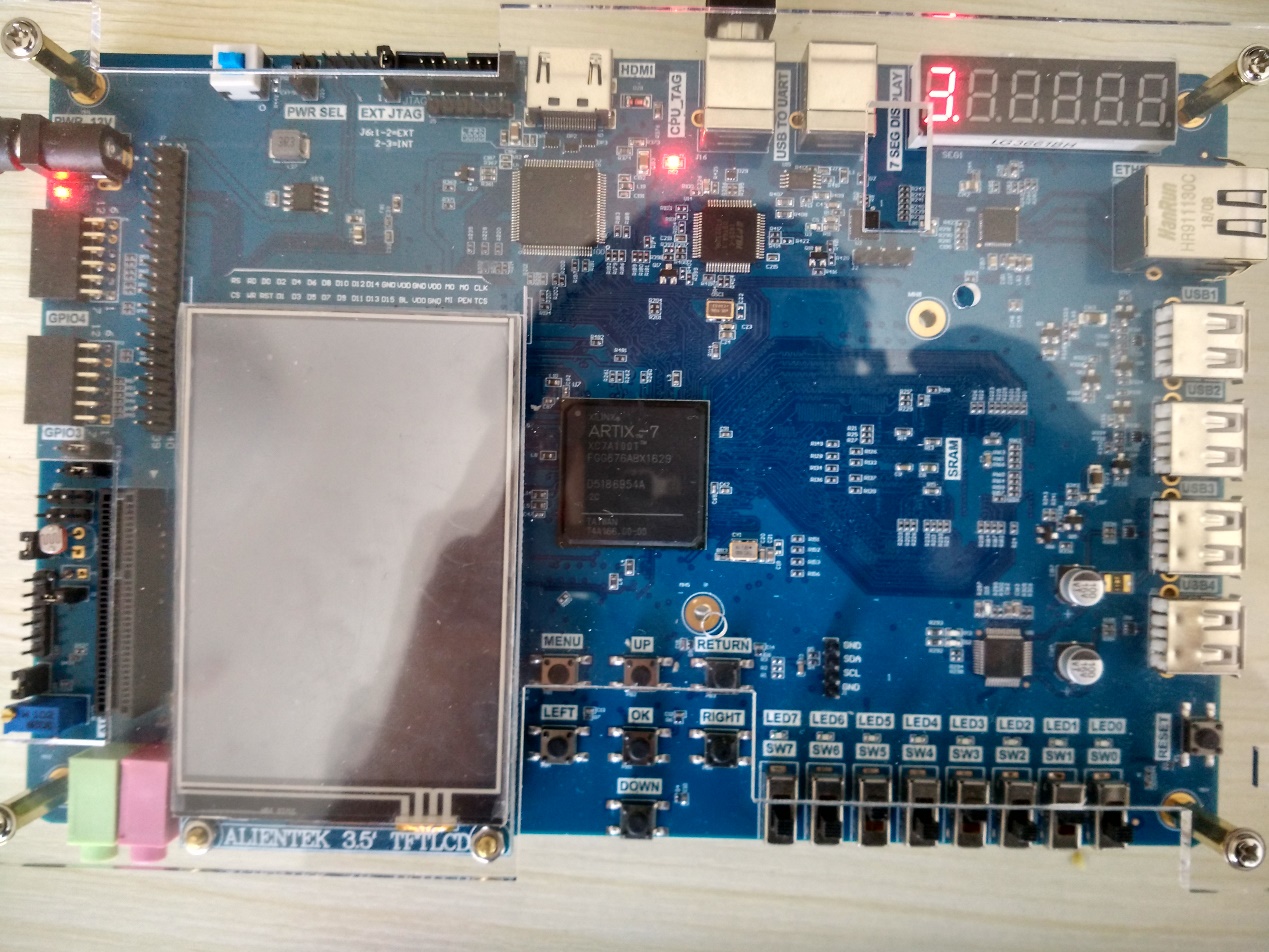

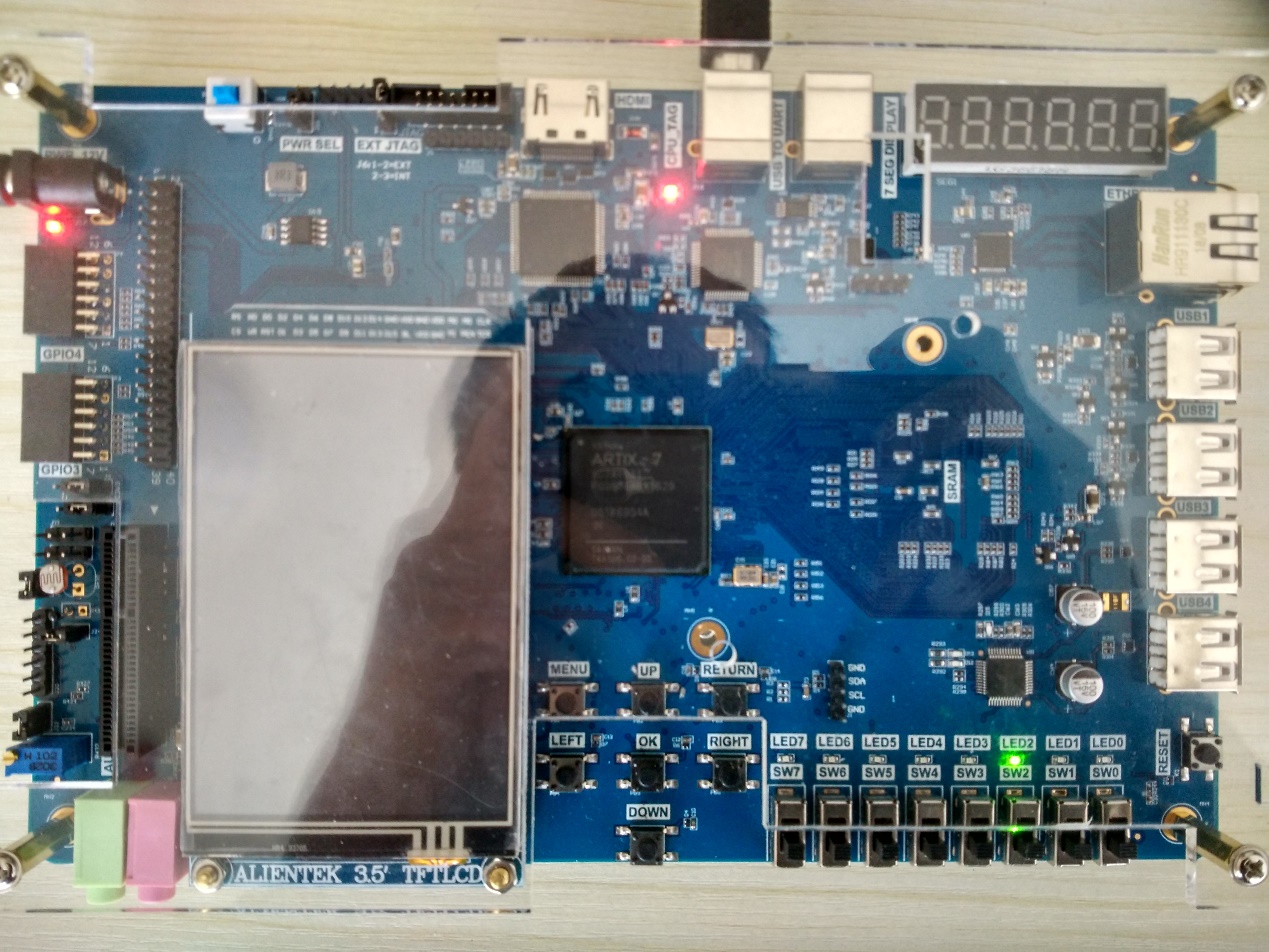

6.Download to the develop board to test and dial the DIP switch to see the corresponding LED light on and off. See Fig 2. 2.

Fig 2. 2 Experiment result

7.Use of ILA

- Choose top-level entity SW_LED.v file to Run Synthesis

- After the integration is complete, under the Netlist window, all network nodes present in the current design are listed. Debug the network nodes. See Fig 2. 3.

Fig 2. 3 Mark debugged network nodes

-

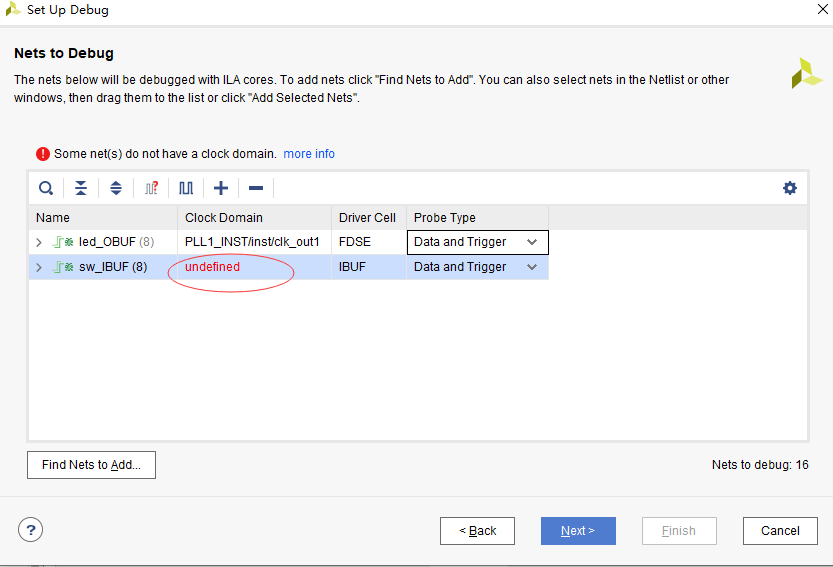

- In the Vivado main interface menu, execute the menu command Tool -> Set up Debug. In the popup window, there is clock domain of the selected debug signal. The clock domain of sw_IBUF is red. See Fig 2. 4.

Fig 2. 4 Debugged network node clock domain setting

-

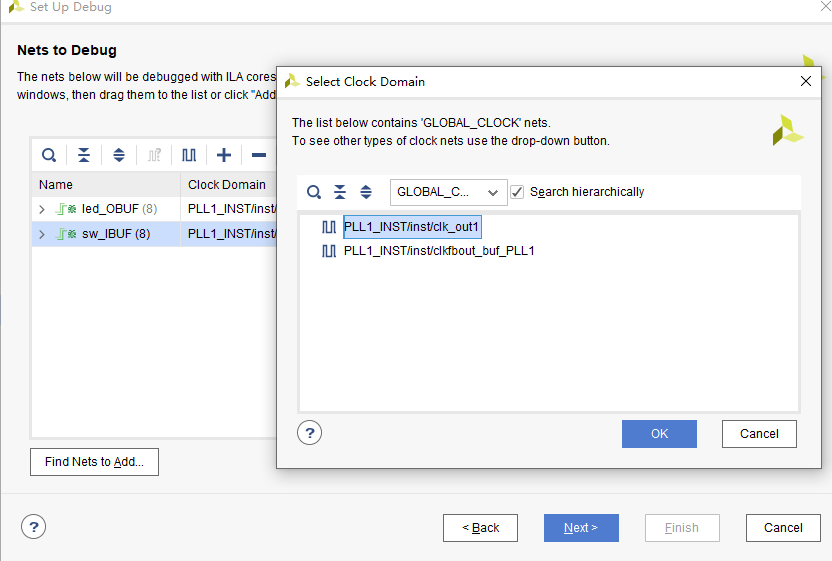

- In the red circle shown in Fig 2. 4, right click to set the clock domain.

Fig 2. 5 Modify the debugged network node clock domain

-

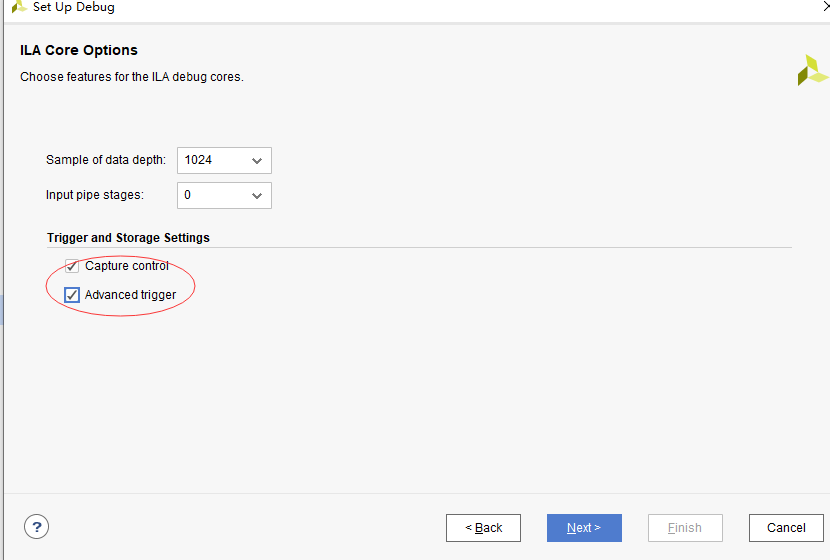

- After the setting is completed, click Next. The popup window is shown in Fig 2. 6. Set the data collection depth and select the check box in front of Capture control and Advance trigger. Then keep clicking Next until the end.

Fig 2. 6 Set the data collection depth

-

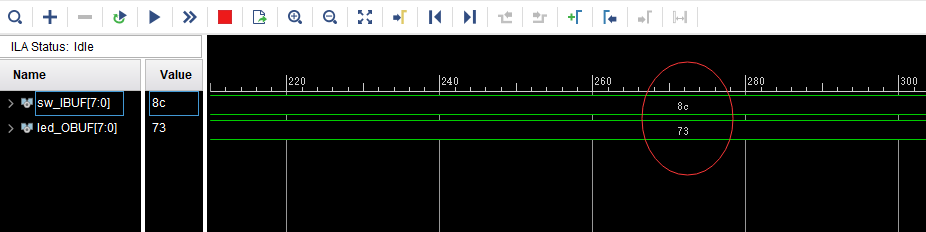

- Add I/O pin constraint information for implementation. Then generate a bit file and download it to FPGA. The debugging interface is automatically popped up. Click the icon button to see the following results. The test results in the debug diagram below Fig 2. 7 indicate that the design results are correct.

Fig 2. 7 Debug

When the input of switch is high, the input LED pin is controlled to be low, and the LED is lit. The figure for the experiment result on board from above shows that the input sw is 10001100 and the LED light is 01110011. The hexadecimal is 8c and 73 respectively. It is consistent with the ILA test results in the figure above.

- Modify the trigger condition to test the output under different trigger conditions

Experiment 3 Basic Digital Clock Experiment and Programming of FPGA Configuration Files

1.Experiment Objective

-

- Review the contents of experiment 1 and experiment 2, master the configuration of PLL, the design of frequency divider, the principle of schematics and the pin assignment of FPGA.

- Study BCD decoder

- Display design of 4-digit hexadecimal to 7 segment display decoders

- Generate a programmable configuration file and program it to the serial FLASH of the development board through the JTAG interface.

2.Design of The Experiment

-

- Refer experiment 1 for building new projects, chip selection

| module BCD_counter(

input rst, input inclk, //c0_50Mclk output reg [7:0] seven_seg, output reg [3:0] scan ); wire sys_clk; wire pll_locked; reg sys_rst; reg ext_rst;

always@(posedge sys_clk) begin sys_rst<=!pll_locked; ext_rst<=rst; end |

-

- Add PLL, the input clock is 50 MHz, and the output clock is 100 MHz. Refer experiment 1 for more information

| BCD_counterPLL1 BCD_counterPLL1_inst

( .areset(1’b0), .inclk0(inclk), .c0(sys_clk), .locked(pll_locked) ); |

-

- Add microsecond, millisecond, and second frequency dividers. Refer to experiment 1.

| reg [7:0] us_reg;

reg [9:0] ms_reg; reg [9:0] s_reg; reg us_f,ms_f,s_f,min_f;

always@(posedge sys_clk) //Microsecond frequency division if(sys_rst) begin us_reg<=0; us_f<=1’b0; end else begin us_f<=1’b0; if(us_reg==99)begin us_reg<=0; us_f<=1’b1; end else begin us_reg<=us_reg+1’b1; end end always@(posedge sys_clk) if(sys_rst) begin ms_reg<=0; ms_f<=1’b0; end else begin ms_f<=1’b0; if(us_f)begin if(ms_reg==999)begin ms_reg<=0; ms_f<=1’b1; end else ms_reg<=ms_reg+1’b1; end End always@(posedge sys_clk) if(sys_rst) begin s_reg<=0; s_f<=1’b0; end else begin s_f<=1’b0; if(ms_f)begin if(s_reg==999)begin s_reg<=0; s_f<=1’b1; end else s_reg<=s_reg+1’b1; end end |

-

- Minute and second frequency divider

| always@(posedge sys_clk) //Second frequency division

if(!ext_rst)begin counta<=0; countb<=0; min_f <=1’b0; end else begin min_f <=1’b0; if(s_f) begin if(counta==4’d9) begin counta<=4’d0; if(countb==5)begin countb<=0; min_f<=1’b1; end else countb<=countb+1’b1; end else begin counta<=counta+1’b1; end end end

always@(posedge sys_clk) //Minute frequency division if(!ext_rst)begin countc<=4’d0; countd<=4’d0; end else begin if(min_f) begin if(countc==4’d9) begin countc<=4’d0; if(countd==5)begin countd<=0; end else countd<=countd+1’b1; end else begin countc<=countc+1’b1; end end end |

-

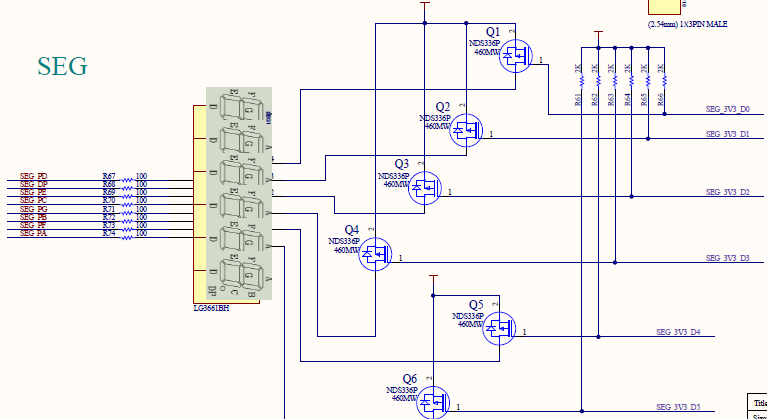

- Learn the schematics of the common anode segement decoder and the connection between the scanning circuit and the FPGA.

Fig 3. 1 Common anode segment decoder schematics

-

-

- The pins of segment display decoder are shown in Fig 3. 1. This is a schematic diagram of the six decoders combined. The pin names A, B, C, D, E, F, and G (corresponding connections are SEG_PA, SEG_PB, SEG_PC, SEG_PD, SEG_PE, SEG_PF, SEG_PG) correspond to the 7 segments of the decoder, and the DP (corresponding connection is SEG_PD)corresponds to the 8th segment, which is commonly used as a decimal point display.

-

A, B, C, D, E, F, G, D, P select which segment of the decoder will lit. The segment to be lit corresponds to the low point.

Illumination of segment decoders is controlled by the bit selection lines SEG_3V3_D0, SEG_3V3_D1, SEG_3V3_D2, SEG_3V3_D3, SEG_3V3_D4, SEG_3V3_D5.

-

-

- Code for the segment display decoder

-

| always@(*)

case(count_sel) 0:seven_seg_r<=7’b100_0000; 1:seven_seg_r<=7’b111_1001; 2:seven_seg_r<=7’b010_0100; 3:seven_seg_r<=7’b011_0000; 4:seven_seg_r<=7’b001_1001; 5:seven_seg_r<=7’b001_0010; 6:seven_seg_r<=7’b000_0011; 7:seven_seg_r<=7’b111_1000; 8:seven_seg_r<=7’b000_0000; 9:seven_seg_r<=7’b001_0000; default:seven_seg_r<=7’b100_0000; endcase always@(posedge sys_clk) seven_seg<={1’b1,seven_seg_r}; |

-

-

- Dynamic canning

-

The dynamic scanning of the segment display decoder utilizes the visual persistence characteristic of the human eye, and in addition to the speed of change that the human eye can distinguish, the segment corresponding to each decoder is quickly and time-divisionally illuminated. Because the time taken to illuminate all the decoders is less than the visual persistence of the human eye, in the eyes of the people, these decoders are continuously lit at the same time, and there is no feeling of flickering.

| reg [1:0] scan_st;

always@(posedge sys_clk) if(!ext_rst) begin scan <=4’b1111; count_sel <=4’d0; scan_st<=0; end else case(scan_st) 0:begin scan <=4’b1110; count_sel<=counta; if(ms_f) scan_st<=1; end 1:begin scan <=4’b1101; count_sel <=countb; if(ms_f) scan_st <=2; end 2:begin scan<=4’b1011; count_sel <=countc; if(ms_f) scan_st<=3; end 3:begin scan<=4’b0111; count_sel<=countd; if(ms_f) scan_st<=0; end default:scan_st<=0; endcase |

3.FPGA Pin Assignment

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk | System clock 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| seven_seg[0] | Segment a | SEG_PA | K26 |

| seven_seg[1] | Segment b | SEG_PB | M20 |

| seven_seg[2] | Segment c | SEG_PC | L20 |

| seven_seg[3] | Segment d | SEG_PD | N21 |

| seven_seg[4] | Segment e | SEG_PE | N22 |

| seven_seg[5] | Segment f | SEG_PF | P21 |

| seven_seg[6] | Segment g | SEG_PG | P23 |

| seven_seg[7] | Segment h | SEG_DP | P24 |

| scan[0] | Segment 1 | SEG_3V3_D0 | R16 |

| scan[1] | Segment 2 | SEG_3V3_D1 | R17 |

| scan[2] | Segment 3 | SEG_3V3_D2 | N18 |

| scan[3] | Segment 4 | SEG_3V3_D3 | K25 |

-

- Lock the pin, compile, and download the program to the develop board

- Observe the test result

Fig 3. 2 Segment decoder illuminates

4.Configure the Serial Flash Programming

-

- The schematics of configuring serial Flash is as follows:

Figure 3. 3 Schematics of Serial Flash interface

-

- Configure FLASH and FPGA pin mapping

| FLASH | *SPI_CS_N | SPI_SO | *SPI_WP_N | SPI_IO | SPI_SCLK | *SPI_HOLD |

| FPGA PINS | P18 | R15 | P14 | R14 | M22 | N14 |

* SPI_CS_N, SPI_WP_N, SPI_HOLD must be connected to pull-up resistors

-

- FPGA configuration mode

-

- Configure the circuit, the resistor with the * mark in it is not soldered when the device is assembled, so the configuration circuit is selected as MSEL=0010, as shown in Table above.

Fig 3. 4 Configuration option

-

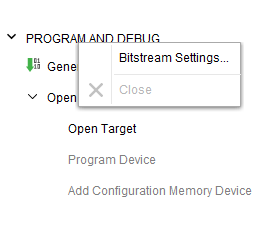

- Generate a readable configuration file

- See Fig 3. 5, right click on PROGRAM AND DEBUG to pop up the bitstream setting option.

- Generate a readable configuration file

Fig 3. 5 Bit file generation setting

-

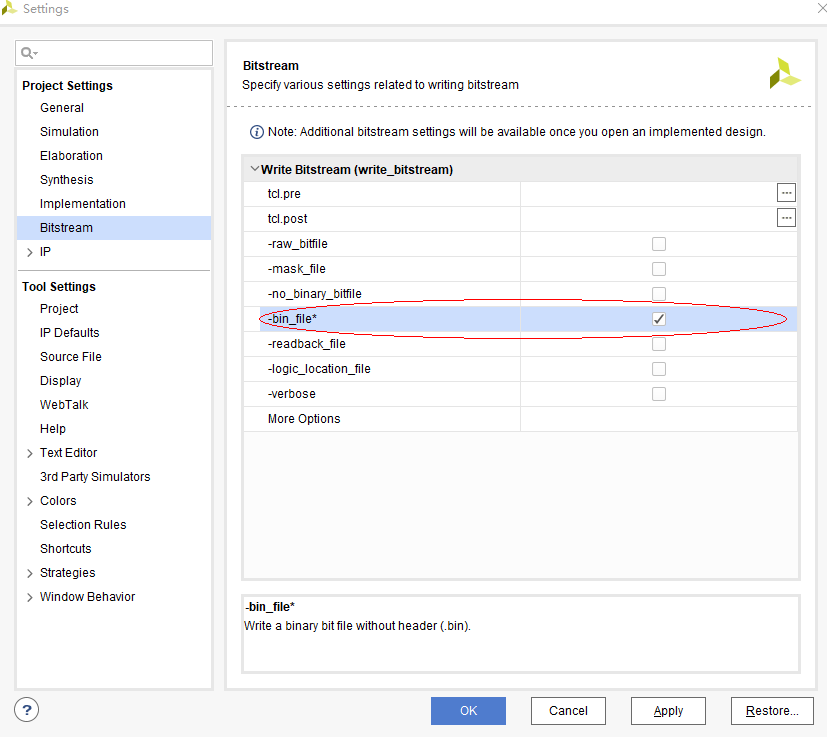

-

- Click Bitstream setting, tick bin_file*, click OK. See Fig 3. 6.

-

Fig 3. 6 Bin file generation setting

-

-

- See Fig 3. 7, click Generate Bitstream to generate the bit file and bin file. Click Open Hardware Manager to connect the board

-

Fig 3. 7 Bit file generation

-

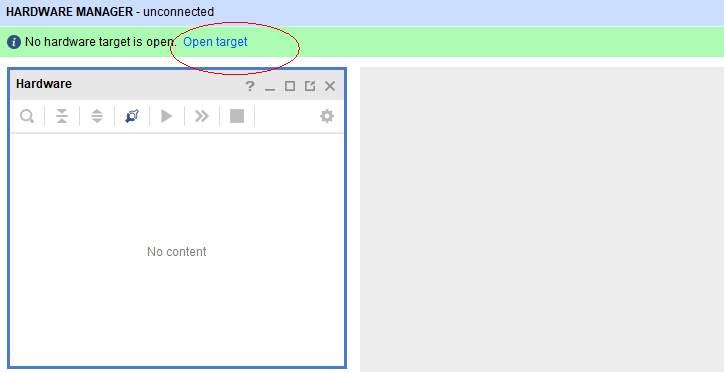

-

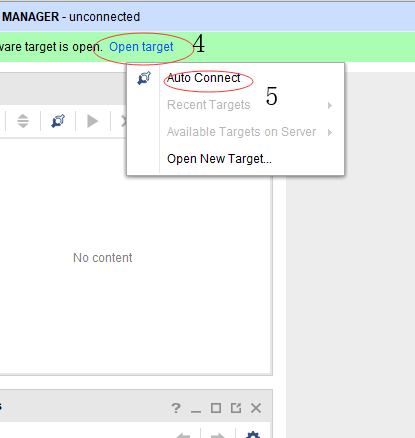

- Click Open target to connect with the board. See Fig 3. 8.

-

Fig 3. 8 Connect to the develop board

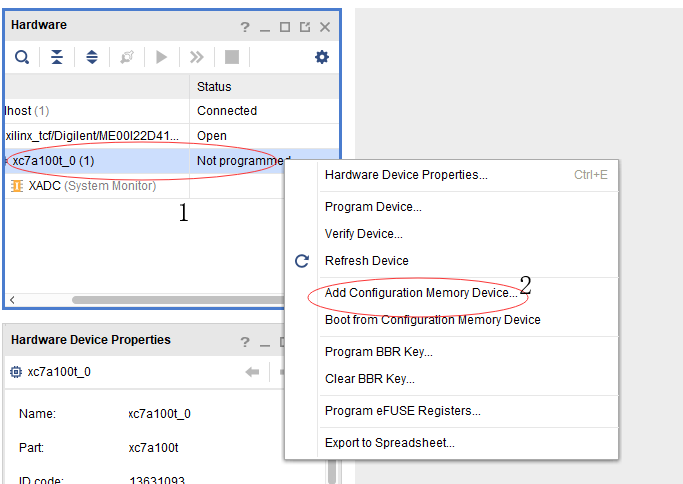

- Select the chip in step 1, right click to choose Add Configuration Memory Device in step 2. See Fig 3. 9.

Fig 3. 9 Adding memory device

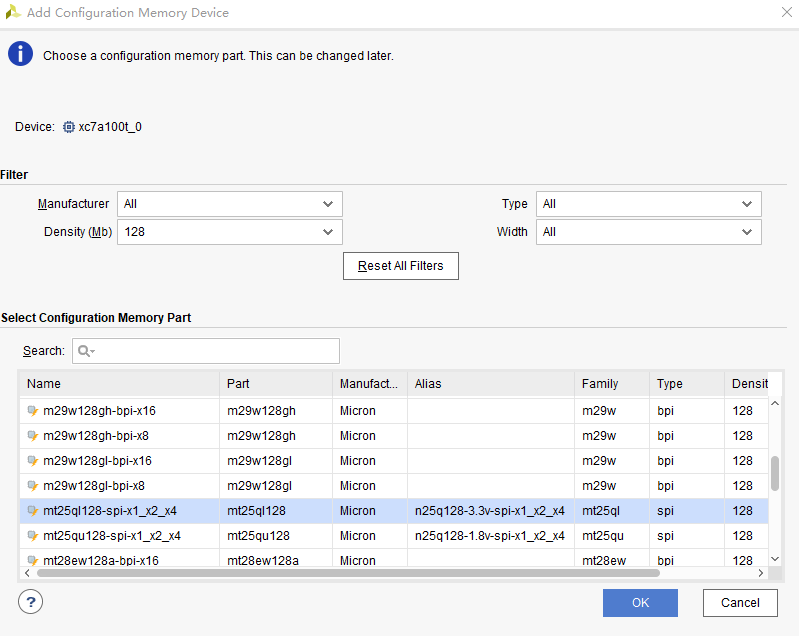

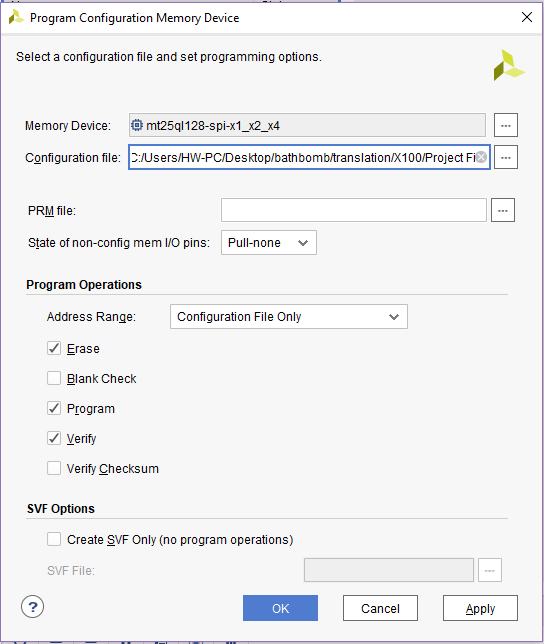

- Choose the Flash chip to be mt25ql128, then click OK. See Fig 3. 10.

Fig 3. 10 Select Flash part

- Add bin file to be the Configuration file.

Fig 3. 11 Add the bin file

- The test result is shown in Fig 3. 12.

Fig 3. 12 Test result

Experiment 4 Block/SCH Digital Clock Design

1.Experiment Objective

-

- Review the new FPGA project building in Vivado, device selection, PLL creation, PLL frequency setting, Verilog tree hierarchy design, and the use of ILA

- Master the design method of graphics from top to bottom

- Combine the BCD_counter project to realize the movement of the decimal point (DP) of the decoder

- Observe the test result

2.Experiment Procedure

- File -> Project -> New

Select Device: XC7A100T-2FGG676I

- See Fig 4. 1, add source file, new top-level entity: block_counter.v

Fig 4. 1 Build source file

- As shown in Fig 4. 2, add the PLL as in the experiment 1, set the input clock to 50 MHz, and the output clock to 100 MHz.

Fig 4. 2 Set the PLL IP core

- Create a new Verilog HDL file for the frequency divider

- Divide the 100 MHz clock into a 1 MHz clock

| module div_us(

input rst, input sys_clk, output reg us_f ); reg[6:0] us_r; always@(posedge sys_clk) if(rst)begin us_r<=0; us_f<=1’b0; end else begin us_f<=1’b0; if(us_r==99)begin us_r<=0; us_f<=1’b1; end else begin us_r<=us_r+1; end end endmodule |

-

- Create a new 1000 division verilog HDL file again, div_1000f.v

| module div_1000f

( input rst, input sys_clk, input in_f, output reg div1000_f ); reg[9:0] div1000_r; always@(posedge sys_clk) if(rst)begin div1000_r<=9’d0; div1000_f<=1’b0; end else begin div1000_f<=1’b0; if(in_f) begin if(div1000_r==999)begin div1000_r<=0; div1000_f<=1’b1; end else begin div1000_r<=div1000_r+1; end end end endmodule |

- Use the 1000 frequency division program div_1000f.v to divide the 1 MHZ clock into 1000 HZ, 1 HZ clock.

| module block_div(

input wire sys_clk, input wire sys_rst,

output wire us_f, output wire ms_f, output wire s_f );

div_us div_us_inst( .rst (sys_rst), .sys_clk (sys_clk) , .us_f (us_f) );

div_1000f div_1000f_inst( .rst (sys_rst) , .sys_clk (sys_clk) , .in_f (us_f ) , .div1000_f (ms_f) );

div_1000f div_1000f_inst2( .rst (sys_rst) , .sys_clk (sys_clk) , .in_f (ms_f ) , .div1000_f (s_f) );

endmodule |

- Create a new Verilog file bcd_counter.v, design hour counter and minute counter

| module bcd_counter(

input rst, input sys_rst, input sys_clk, input ms_f, input s_f, output reg [7:0] seven_seg, output reg [3:0] scan ); reg ext_rst; reg min_f;

reg [3:0] counta,countb; reg [3:0] countc,countd; reg [3:0] count_sel;

reg [6:0]seven_seg_r;

always@(posedge sys_clk) begin ext_rst<=sys_rst; end

always@(posedge sys_clk) if(ext_rst)begin counta<=0; countb<=0; min_f <=1’b0; end else begin min_f <=1’b0; if(s_f) begin if(counta==4’d9) begin counta<=4’d0; if(countb==5)begin countb<=0; min_f<=1’b1; end else countb<=countb+1’b1; end else begin counta<=counta+1’b1; end end

end always@(posedge sys_clk) if(ext_rst)begin countc<=4’d0; countd<=4’d0; end else begin if(min_f) begin if(countc==4’d9) begin countc<=4’d0; if(countd==5)begin countd<=0; end else countd<=countd+1’b1; end else begin countc<=countc+1’b1; end end

end

reg [1:0] scan_st;

always@(posedge sys_clk) if(ext_rst) begin scan <=4’b1111; count_sel <=4’d0; scan_st<=0; end else case(scan_st) 0:begin scan <=4’b1110; count_sel <=counta; if(ms_f) scan_st <=1; end 1:begin scan <=4’b1101; count_sel <=countb; if(ms_f) scan_st <=2; end 2:begin scan<=4’b1011; count_sel <=countc; if(ms_f) scan_st<=3; end 3:begin scan<=4’b0111; count_sel <=countd; if(ms_f) scan_st<=0; end default:scan_st<=0; endcase

always@(*) case(count_sel) 0:seven_seg_r<=7’b100_0000; 1:seven_seg_r<=7’b111_1001; 2:seven_seg_r<=7’b010_0100; 3:seven_seg_r<=7’b011_0000; 4:seven_seg_r<=7’b001_1001; 5:seven_seg_r<=7’b001_0010; 6:seven_seg_r<=7’b000_0011; 7:seven_seg_r<=7’b111_1000; 8:seven_seg_r<=7’b000_0000; 9:seven_seg_r<=7’b001_0000; default:seven_seg_r<=7’b100_0000; endcase always@(posedge sys_clk) seven_seg<={1’b1,seven_seg_r};

endmodule |

- Instantiate each function module subroutine into the top-level entity for comprehensive compilation.

| module block_counter(

input wire rst, input wire clk_in,

output wire [7:0] seven_seg, output wire [3:0] scan );

wire us_f; wire ms_f ; wire s_f ;

reg sys_rst; wire sys_clk;

block_div block_div_inst( .sys_clk (sys_clk) , .sys_rst (sys_rst) , .us_f (us_f) , .ms_f (ms_f) , .s_f (s_f) ); always @(posedge sys_clk) sys_rst <=!locked ; pll pll_inst ( // Clock out ports .clk_out1(sys_clk), // output clk_out1 // Status and control signals .reset(1’b0), // input reset .locked(locked), // output locked // Clock in ports .clk_in1(clk_in)); // input clk_in1

bcd_counter bcd_counter_inst( .rst (rst) , .sys_rst (sys_rst) , .sys_clk (sys_clk) , //c0_50Mclk .ms_f (ms_f) , .s_f (s_f) , .seven_seg (seven_seg) , .scan (scan) ); endmodule |

- Lock the Pin

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk_in | Sytem clock 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| seven_seg[0] | Segment a | SEG_PA | K26 |

| seven_seg[1] | Segment b | SEG_PB | M20 |

| seven_seg[2] | Segment c | SEG_PC | L20 |

| seven_seg[3] | Segment d | SEG_PD | N21 |

| seven_seg[4] | Segment e | SEG_PE | N22 |

| seven_seg[5] | Segment f | SEG_PF | P21 |

| seven_seg[6] | Segment g | SEG_PG | P23 |

| seven_seg[7] | Segment h | SEG_DP | P24 |

| scan[0] | Segment 6 | SEG_3V3_D5 | T24 |

| scan[1] | Segment 5 | SEG_3V3_D4 | R25 |

| scan[2] | Segment 4 | SEG_3V3_D3 | K25 |

| scan[3] | Segment 3 | SEG_3V3_D2 | N18 |

- Compile, download to the board and test the program. The test result is shown in Fig 4. 3.

Fig 4. 3 Test result

3.More to Practice

-

-

- Practice the design of high-level digital clocks, month (positional system by base 30), day (positional system by base 24), hour (sexagesimal), and minute (sexagesimal).

- The content of this lab exercise is to use the design with a top-down design approach.

-

Experiment 5 Button Debounce Design and Experimental Experiment

1.Experiment Objective

-

- Review the design of blinking LED

- Learn the principle of button debounce, and adaptive programming

- Learn the connection and use of the FII-PRX100T button schematics

- Integrated application of button debounce and another compatible program design

2.Experiment

- Button debounce principle

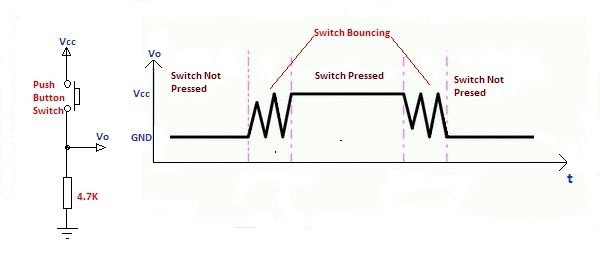

Usually, the switches used for the buttons are mechanical elastic switches. When the mechanical contacts are opened and closed, due to the elastic action of the mechanical contacts, a push button switch does not immediately turn on when closed, nor is it off when disconnected. Instead, there is some bouncing when connecting and disconnecting. See Fig 5. 1

Fig 5. 1 Button bounce principle

The length of the button’s stable closing time is determined by the operator. It usually takes more than 100ms. If you press it quickly, it will reach 40-50ms. It is difficult to make it even shorter. The bouncing time is determined by the mechanical characteristics of the button. It is usually between a few milliseconds and tens of milliseconds. To ensure that the program responds to the button’s every on and off, it must be debounced. When the change of the button state is detected, it should not be immediately responding to the action, but waiting for the closure or the disconnection to be stabilized before processing. Button debounce can be divided into hardware debounce and software debounce.

In most of cases, we use software or programs to achieve debounce. The simplest debounce principle is to wait for a delay time of about 10ms after detecting the change of the button state, and then perform the button state detection again after the bounce disappears. If the state is the same as the previous state just detected, the button can be confirmed. The action has been stabilized. This type of detection is widely used in traditional software design. However, as the number of button usage increases, or the buttons of different qualities will react differently. If the delay is too short, the bounce cannot be filtered out. When the delay is too long, it affects the sensitivity of the button.

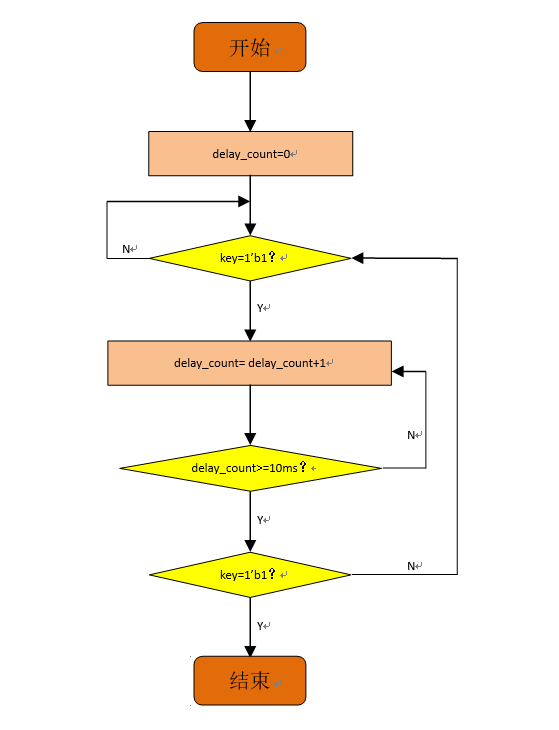

This chapter introduces an adaptive button debounce method: starts timing when a change in the state of the button is detected. If the state changes within 10ms, the button bouncing exists. It returns to the initial state, clears the delay counter, and re-detects the button state until the delay counter counts to 10ms. The same debounce method is used for pressing and releasing the button. The flow chart is shown in Fig 5. 2.

- Code for button debouncing

Verilog code is as follows:

| module pb_ve(

input sys_clk, //100 MHz input sys_rst,//System reset input ms_f, //millisecond pulse input keyin, //input state of the key output keyout //Output status of the key. Every time releasing the button, only one system ); //clock pulase outputs

reg keyin_r; //Input latch to eliminate metastable reg keyout_r;//Output pulse //push_button vibrating elemination reg [1:0] ve_key_st; //State machine status bit reg [3:0] ve_key_count;//delay counter

always@(posedge sys_clk) keyin_r<=keyin; // Input latch to eliminate metastable

always@(posedge sys_clk) if(sys_rst) begin keyout_r <=1’b0; ve_key_count <=0; ve_key_st <=0; end else case(ve_key_st) 0:begin keyout_r<=1’b0; ve_key_count <=0; if(!keyin_r) ve_key_st <=1; end 1:begin if(keyin_r) ve_key_st <=0; else begin if(ve_key_count==10) begin ve_key_st <=2; end else if(ms_f) ve_key_count<=ve_key_count+1; end end 2:begin ve_key_count <=0; if(keyin_r) ve_key_st <=3; end 3:begin if(!keyin_r) ve_key_st <=2; else begin if(ve_key_count==10) begin ve_key_st <=0; keyout_r<=1’b1;//After releasing debounce, output a synchronized end //clock pulse else if(ms_f) ve_key_count<=ve_key_count+1;

end end default:; endcase assign keyout=keyout_r; endmodule |

Case 0 and 1 debounce the button press state. Case 2 and 3 debounce the button release state. After finishing the whole debounce procedure, the program outputs a synchronized clock pulse.

- Button debounce flow chart

End

Start

Fig 5. 2 Button debounce flow chart

- Combine running LED design and modify the button debounce.

- Build new project

- Create a PLL symbol

- Create a button debounce symbol (See the Verilog HDL code in this experiment)

- Create a top-level file key_filter

| module key_filter(

input clk_in, input left, input right, input wire rst, output wire [7:0] led

); wire sys_rst_s= sys_rst; reg sys_rst; wire ms_f; wire s_f ; wire sys_clk; wire locked; wire left_flag, right_flag ; reg left_cmd=0; reg right_cmd =0; block_counter block_counter_inst(

. sys_rst ( sys_rst_s), . sys_clk (sys_clk), . ms_f(ms_f), . s_f (s_f) ); LED_shifting LED_shifting_inst ( . rst(sys_rst_s) , . sys_clk(sys_clk), .key_left(left_cmd), .key_right(right_cmd), .s_f(s_f), . led(led) ); pb_ve pb_ve_inst1( .sys_clk (sys_clk), .sys_rst (sys_rst_s), .ms_f (ms_f ), .keyin (left ), .keyout (left_flag ) ); pb_ve pb_ve_inst2( .sys_clk (sys_clk), .sys_rst (sys_rst_s), .ms_f (ms_f ), .keyin (right ), .keyout (right_flag ) ); always @ ( posedge sys_clk ) if (sys_rst_s) {right_cmd,left_cmd}<=2’b00; else begin case({right_flag,left_flag}) 0: {right_cmd,left_cmd}<={right_cmd,left_cmd}; 1: {right_cmd,left_cmd}<=2’b01; 2: {right_cmd,left_cmd}<=2’b10; 3: {right_cmd,left_cmd}<={right_cmd,left_cmd}; endcase end always @ (posedge sys_clk ) sys_rst<=!locked; pll pll_inst( .clk_out1(sys_clk), .reset(!rst), .locked(locked), .clk_in1(clk_in) );

endmodule |

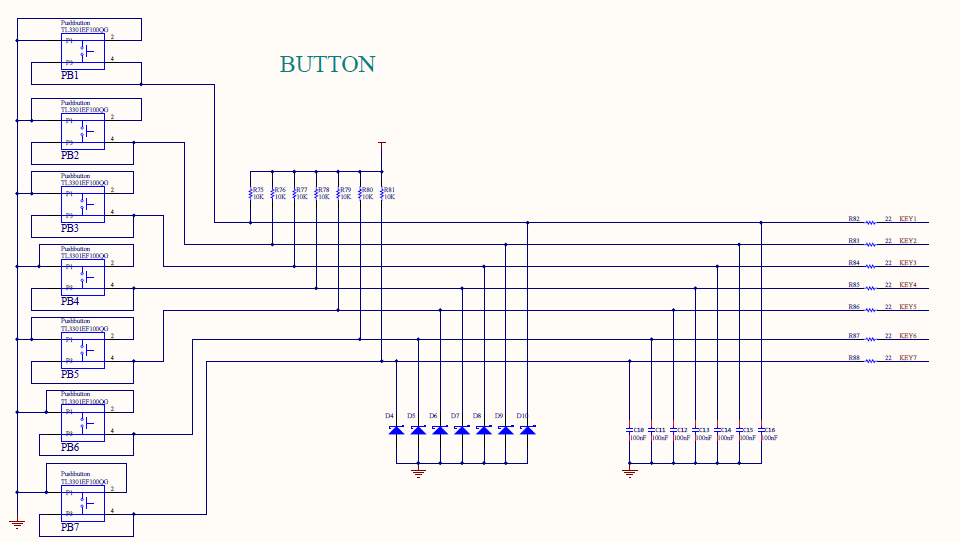

3.Hardware Design

- Button schematics

Fig 5. 4 Button schematics

- FPGA pin mapping

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk_in | System clock 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| led0 | LED 0 | LED0 | N17 |

| led1 | LED 1 | LED1 | M19 |

| led2 | LED 2 | LED2 | P16 |

| led3 | LED 3 | LED3 | N16 |

| led4 | LED 4 | LED4 | N19 |

| led5 | LED 5 | LED5 | P19 |

| led6 | LED 6 | LED6 | N24 |

| led7 | LED 7 | LED7 | N23 |

| left | Press left | KEY4 | K5 |

| right | Press right | KEY6 | P1 |

-

- Compile and debug

- Download the program to the board and observe the test result. See Fig 5. 5

Fig 5. 5 Test Result

- Observe the test results. By default, 8 LEDs are off. Press the left button to switch the flow mode on the left side of the LED. Press the right button on the right side of the LED to switch between the flow mode. While holding down the left and right buttons, the LED remains in its original state.

Experiment 6 Digital Clock Comprehensive Design Experiment

1.Experiment Objective

-

- Design month, day, hour, minute, and second digital clock experiments, using 6 segment decoders

-

-

- 60 seconds carried to the minute

- 60 minutes carried to the hour

- 24 hours carried to the day

- 30 days carried to the month, and reset all

-

-

- Set four keys: menu, left, up, down

- The menu key controls the calibration function to switch between clock, date, and alarm.

- The left key selects which value is currently calibrated

- The Up and down keys add 1 and subtract 1 calibration to the data to be calibrated requires that the corresponding segment decoder is flashed.

- Modulate the design so that it can be reused

- Learn to use the module parameters

- Learn to use the timing analysis function of Vivado and correctly constrain the clock signal

- Design month, day, hour, minute, and second digital clock experiments, using 6 segment decoders

2.Design Procedure

- Build new project

-

- Project name is calendar_counter

- Select the device XC7A100TFGG676-2

- The top-level entity is calendar_counter.bdf or calendar_counter.v (Here the Verilog file is used)

-

- Design and integrate of submodule

-

- PLL module

- Frequency divider

- Button debounce module

- Counting module dual_num_count.v

-

Design a universal 2-bit counter that uses the parameter to specify the specified count setting.

| Module dual_num_count

#(parameter PAR_COUNTA=9, parameter PAR_COUNTB=5 ) ( input i_sys_clk, input i_ext_rst, input i_adj_up, input i_adj_down, input [1:0] i_adj_sel, input i_trig_f, output reg o_trig_f, output reg [3:0] o_counta, output reg [3:0] o_countb ); always@(posedge i_sys_clk) if(!i_ext_rst)begin o_counta <=0; o_countb <=0; o_trig_f <=1’b0; end else begin o_trig_f<=1’b0; if(i_adj_up)begin if(!i_adj_sel[0])begin if(o_counta==9) o_counta<=0; else o_counta<=o_counta+1; end else if(!i_adj_sel[1]) begin if(o_countb==9) o_countb<=0; else o_countb<=o_countb+1; end end else if(i_adj_down) begin if(!i_adj_sel[0])begin if(o_counta==0) o_counta<=9; else o_counta<=o_counta-1; end else if(!i_adj_sel[1])begin if(o_countb==0) o_countb<=9; else o_countb<=o_countb-1; end end else if(i_trig_f) begin if((o_countb==PAR_COUNTB)&&(o_counta==PAR_COUNTA)) begin o_counta<=4’d0; o_countb<=0; o_trig_f<=1’b1; end else begin if(o_counta==9)begin o_counta<=4’d0; o_countb<=o_countb+1; end else begin o_counta<=o_counta+1; end end end end endmodule |

- Button debounce

| module pb_ve(

input sys_clk, input sys_rst, input ms_f, input keyin, output keyout ); reg keyin_r; reg keyout_r; //push_button vibrating elemination reg [1:0] ve_key_st; reg [3:0] ve_key_count; always@(posedge sys_clk) keyin_r<=keyin; always@(posedge sys_clk) if(sys_rst) begin keyout_r <=1’b0; ve_key_count <=0; ve_key_st <=0; end else case(ve_key_st) 0:begin keyout_r<=1’b0; ve_key_count <=0; if(!keyin_r) ve_key_st <=1; end 1:begin if(keyin_r) ve_key_st <=0; else begin if(ve_key_count==10) begin ve_key_st <=2; end else if(ms_f) ve_key_count<=ve_key_count+1;

end end 2:begin ve_key_count <=0; if(keyin_r) ve_key_st <=3; end 3:begin if(!keyin_r) ve_key_st <=2; else begin if(ve_key_count==10) begin ve_key_st <=0; keyout_r<=1’b1; end else if(ms_f) ve_key_count<=ve_key_count+1; end end default:; endcase assign keyout=keyout_r; endmodule |

- Top-level entity design

|

module calendar_counter(

input rst, input left, //key4 input right, input up, input down, input inclk, //c0_50Mclk output reg [6:0] seven_sega, output reg disp_pa, output reg [5:0] scan );

wire sys_clk; wire pll_locked; reg sys_rst; reg ext_rst;

reg [7:0] us_reg; reg [9:0] ms_reg; reg [9:0] s_reg; reg us_f,ms_f,s_f; wire min_f,hr_f,day_f;

reg [3:0] counta;

wire [3:0] count_secl,count_sech; wire [3:0] count_minl,count_minh; wire [3:0] count_hrl,count_hrh;

wire [3:0] count_dayl,count_dayh;

reg [6:0]seven_seg_ra; reg [7:0]disp_p_r;

wire left_r,right_r; wire up_r,down_r;

always@(posedge sys_clk) begin sys_rst<=!pll_locked; ext_rst<=rst; end

always@(posedge sys_clk) if(sys_rst) begin us_reg<=0; us_f<=1’b0; end else begin us_f<=1’b0; if(us_reg==99)begin us_reg<=0; us_f<=1’b1; end else begin us_reg<=us_reg+1; end

end

always@(posedge sys_clk) if(sys_rst) begin ms_reg<=0; ms_f<=1’b0; end else begin ms_f<=1’b0; if(us_f) begin if(ms_reg==999)begin ms_reg<=0; ms_f<=1’b1; end else ms_reg<=ms_reg+1; end end

always@(posedge sys_clk) if(sys_rst) begin s_reg<=0; s_f<=1’b0; end else begin s_f<=1’b0; if(ms_f)begin if(s_reg==999)begin s_reg<=0; s_f<=1’b1; end else s_reg<=s_reg+1; end end dual_num_count #(.PAR_COUNTA(9), .PAR_COUNTB(5) ) dual_num_count_sec ( .i_sys_clk (sys_clk), .i_ext_rst (ext_rst), .i_adj_up (up_r), .i_adj_down (down_r), .i_adj_sel (disp_p_r[1:0]), .i_trig_f (s_f), .o_trig_f (min_f), .o_counta (count_secl), .o_countb (count_sech) );

dual_num_count #(.PAR_COUNTA(9), .PAR_COUNTB(5) ) dual_num_count_min ( .i_sys_clk(sys_clk), .i_ext_rst (ext_rst), .i_adj_up (up_r), .i_adj_down (down_r), .i_adj_sel (disp_p_r[3:2]), .i_trig_f (min_f), .o_trig_f (hr_f), .o_counta (count_minl), .o_countb (count_minh) );

dual_num_count #(.PAR_COUNTA(3),.PAR_COUNTB(2)) dual_num_count_hr ( .i_sys_clk (sys_clk), .i_ext_rst (ext_rst), .i_adj_up (up_r), .i_adj_down (down_r), .i_adj_sel (disp_p_r[5:4]), .i_trig_f (hr_f), .o_trig_f (day_f), .o_counta (count_hrl), .o_countb (count_hrh) );

dual_num_count #(.PAR_COUNTA(0), .PAR_COUNTB(3) ) dual_num_count_day ( .i_sys_clk (sys_clk), .i_ext_rst (ext_rst), .i_adj_up (up_r), .i_adj_down (down_r), .i_adj_sel (disp_p_r[7:6]), .i_trig_f (day_f), .o_trig_f (), .o_counta (count_dayl), .o_countb (count_dayh) );

always@(posedge sys_clk) if(!ext_rst) begin disp_p_r<=8’b1111_1110; end else begin if(left_r) disp_p_r<={disp_p_r[6:0],disp_p_r[7]}; else if(right_r) disp_p_r<={disp_p_r[0],disp_p_r[7:1]}; end reg [2:0] scan_st;

always@(posedge sys_clk) if(!ext_rst) begin scan<=6’b11_1111; counta<=4’b0; disp_pa<=1’b1; scan_st<=0; end else case(scan_st) 0:begin scan <=6’b11_1110; counta <=count_secl; disp_pa<=disp_p_r[0]; if(ms_f) scan_st<=1; end 1:begin scan<=6’b11_1101; counta<=count_sech; disp_pa<=disp_p_r[1]; if(ms_f) scan_st<=2; end 2:begin scan<=6’b11_1011; counta<=count_minl; disp_pa<=disp_p_r[2]; if(ms_f) scan_st<=3; end 3:begin scan<=6’b11_0111; counta<=count_minh; disp_pa<=disp_p_r[3]; if(ms_f) scan_st<=4; end 4:begin scan<=6’b10_1111; counta<=count_hrl; disp_pa<=disp_p_r[4]; if(ms_f) scan_st<=5; end 5:begin scan<=6’b01_1111; counta<=count_hrh; disp_pa<=disp_p_r[5]; if(ms_f) scan_st<=0; end default:scan_st<=0; endcase

always@(*) case(counta) 0:seven_seg_ra<=7’b100_0000; 1:seven_seg_ra<=7’b111_1001; 2:seven_seg_ra<=7’b010_0100; 3:seven_seg_ra<=7’b011_0000; 4:seven_seg_ra<=7’b001_1001; 5:seven_seg_ra<=7’b001_0010; 6:seven_seg_ra<=7’b000_0010; 7:seven_seg_ra<=7’b111_1000; 8:seven_seg_ra<=7’b000_0000; 9:seven_seg_ra<=7’b001_0000; default:seven_seg_ra<=7’b100_0000; endcase always@(posedge sys_clk) seven_sega<=seven_seg_ra; pb_ve pb_ve_left ( .sys_clk (sys_clk), .sys_rst (sys_rst), .ms_f (ms_f), .keyin (left), .keyout (left_r) );

pb_ve pb_ve_right ( .sys_clk (sys_clk), .sys_rst (sys_rst), .ms_f (ms_f), .keyin (right), .keyout (right_r) ); pb_ve pb_ve_up ( .sys_clk (sys_clk), .sys_rst (sys_rst), .ms_f (ms_f), .keyin (up), .keyout (up_r) ); pb_ve pb_ve_down ( .sys_clk (sys_clk), .sys_rst (sys_rst), .ms_f (ms_f), .keyin (down), .keyout (down_r) );

calendar_pll calendar_pll ( .reset (1’b0), .inclk0 (inclk), .c0 (sys_clk), .locked (pll_locked) );

endmodule |

- Lock the Pins

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk | System clock, 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| seven_seg[0] | Segment a | SEG_PA | K26 |

| seven_seg[1] | Segment b | SEG_PB | M20 |

| seven_seg[2] | Segment c | SEG_PC | L20 |

| seven_seg[3] | Segment d | SEG_PD | N21 |

| seven_seg[4] | Segment e | SEG_PE | N22 |

| seven_seg[5] | Segment f | SEG_PF | P21 |

| seven_seg[6] | Segment g | SEG_PG | P23 |

| seven_seg[7] | Segment h | SEG_DP | P24 |

| scan[0] | Segment 6 | SEG_3V3_D5 | T24 |

| scan[1] | Segment 5 | SEG_3V3_D4 | R25 |

| scan[2] | Segment 4 | SEG_3V3_D3 | K25 |

| scan[3] | Segment 3 | SEG_3V3_D2 | N18 |

| scan[4] | Segment 2 | SEG_3V3_D1 | R17 |

| scan[5] | Segment 1 | SEG_3V3_D0 | R16 |

| left | Left button | KEY4 | K5 |

| right | Right button | KEY6 | P1 |

| up | Up button | KEY2 | L4 |

| down | Bottom button | KEY2 | R7 |

- Compile

- Download the program to the develop board for verification

-

- Observe the test result

- Use the left, right keys to move the decimal point of the segment decoder

- Use up, down keys to calibrate time

-

The test result is shown in Fig 6. 1, displaying time 10:27:05

Fig 6. 1 Test result

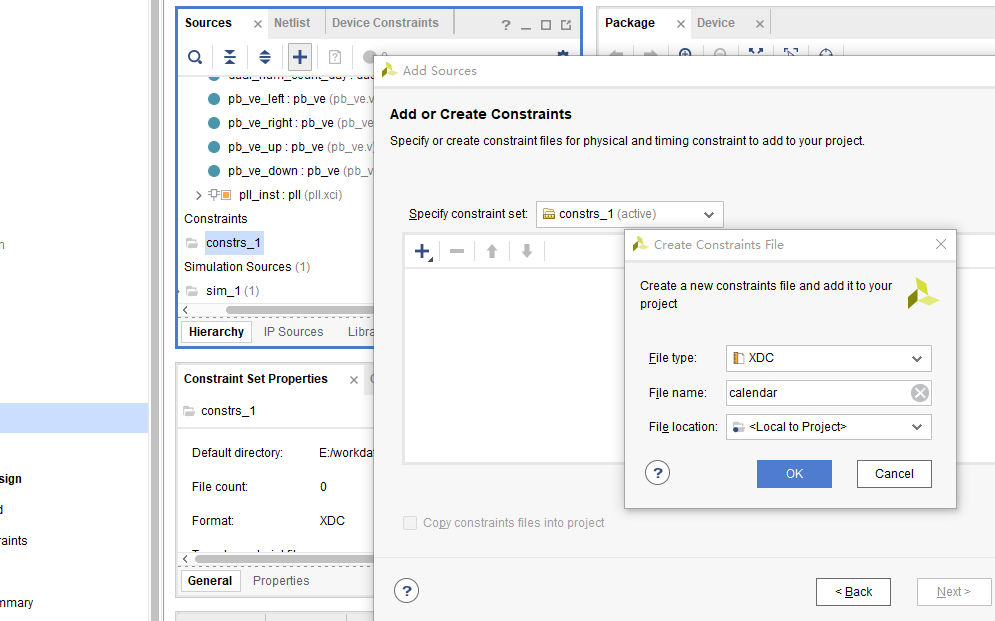

3.Create an XDC File to Constrain the Clock

- Create constrain file

Fig 6. 2 Craete SDC file

XDC file is as follows:

# Create Clock

create_clock -period 20 -name inclk -waveform {0.000 10.000} [get_ports inclk]

- Improve the precision when using up, down to calibrate

-

- The maximum value is automatic recognized, such as in the sexagesimal decimal digit calibration time, if the value reaches 5, the next Up will make the value become 0. When the timing of Down is reduced to 0, the next Down pulse will automatically change to 5.

- Compile, and download the program to the develop board

- Program to the flash memory

-

Experiment 7 Multiplier Use and ISIM Simulation

1.Experiment Objective

-

- Learn to use multiplier

- Use ISIM to simulate design output

2.Experiment Design

-

- Build new project mult_sim

-

-

- Select device XC7A100TFGG676-2

-

-

- Design implement

- 8×8 multiplier, the first input value is an 8-bit switch, and the second input value is the output of an 8-bit counter.

- Observe the result on Modelsim

- Observe the result on 6 segment decoders

- Design procedure

- Create new file mult_sim.v

- Add PLL,set the input clock to be 50 MHz, and the output clock to be 100 MHz

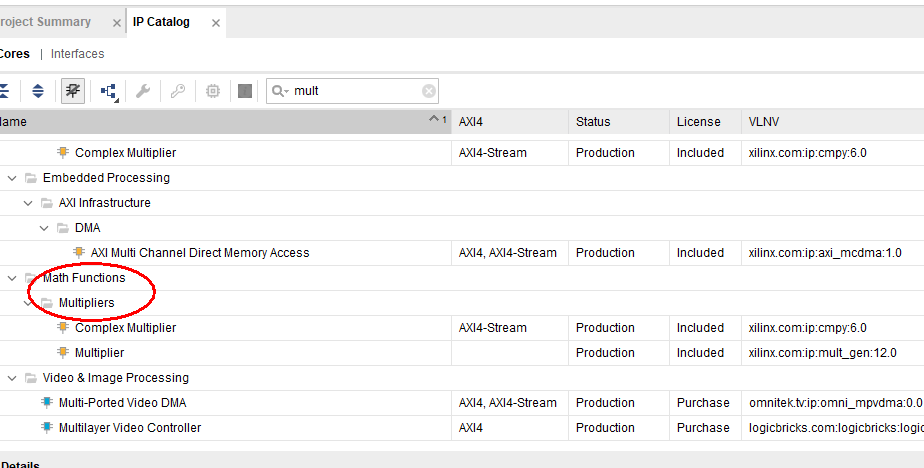

- Add LPM_MULT IP

- Build new project mult_sim

IP Catalog -> input Mult in the search box. Invoke the multipliers. See Fig 7. 1.

Fig 7. 1 Build IP core for multiplier

-

-

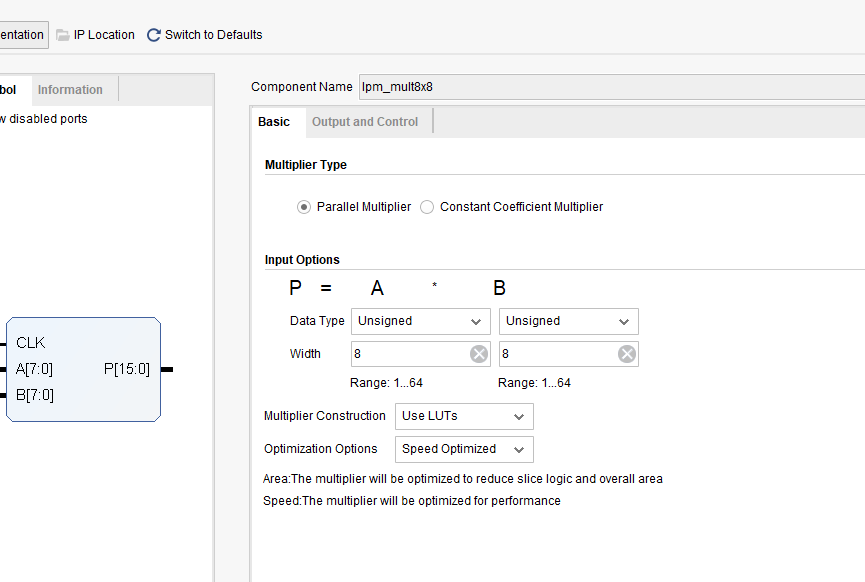

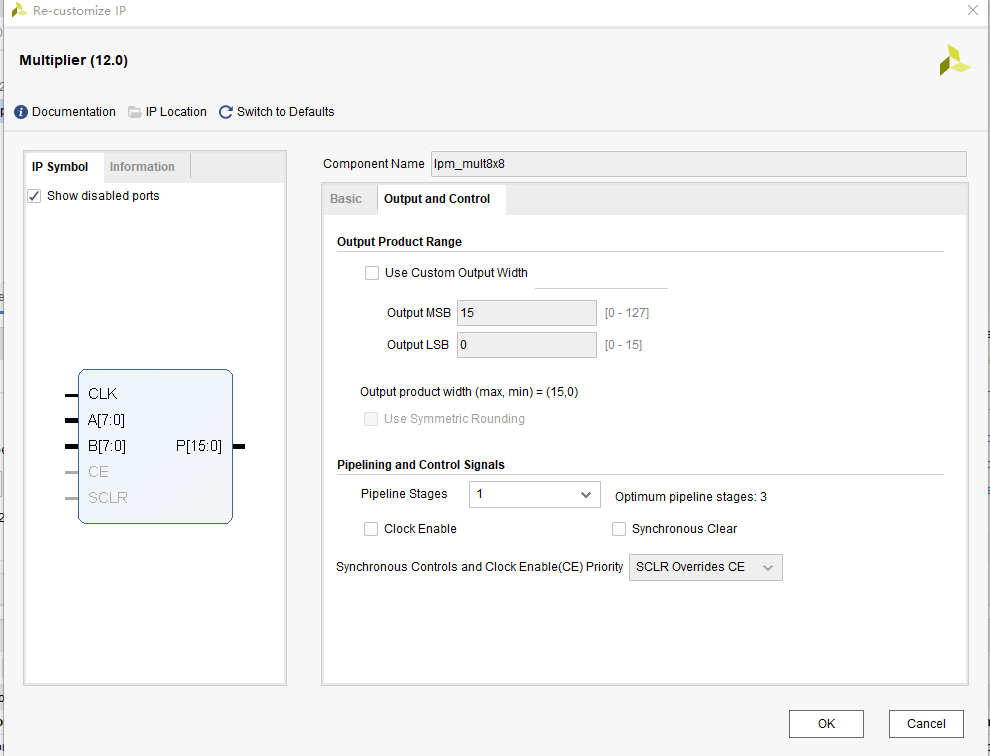

- Choose input data type to be unsigned and width to be 8. See Fig 7. 2.

-

Fig 7. 2 Set the input data type and data width

-

-

- Choose Pipelining and Control Signals. See Fig 7. 3. Add a delay of 1 stage. The default optimum stage is 3 stages.

-

Fig 7. 3 Pipelining setting

-

- Choose default for other settings

- Instantiate in the top-level entity

3.The Top-level Entity Is as Follows:

| module mult_sim

( input rst, input inclk, input [7:0] sw, output [6:0] seven_seg, output [3:0] scan ); wire [15:0] mult_res; wire sys_clk; wire sys_rst; reg [7:0] count; always@(posedge sys_clk) if(sys_rst) count<=0; else count<=count+1; lpm_mult8x8 ( .clock (sys_clk), .dataa (sw), .datab (count), .result (mult_res) ); pll_sys_rst pll_sys_rst_inst ( .inclk (inclk), .sys_clk (sys_clk), .sys_rst (sys_rst) ); endmodule |

4.ISIM Simulation Library Compilation and Call

Under the Vivado platform, you can choose to use built-in simulation tool ISIM or third-party simulation tools for functional simulation of the project. Simulating with the Modelsim simulation tool requires a separate compilation of the simulation library. This routine uses the built-in ISIM tool emulation and briefly introduce Modelsim’s Xilinx simulation library file compilation for simulation using Modelsim.

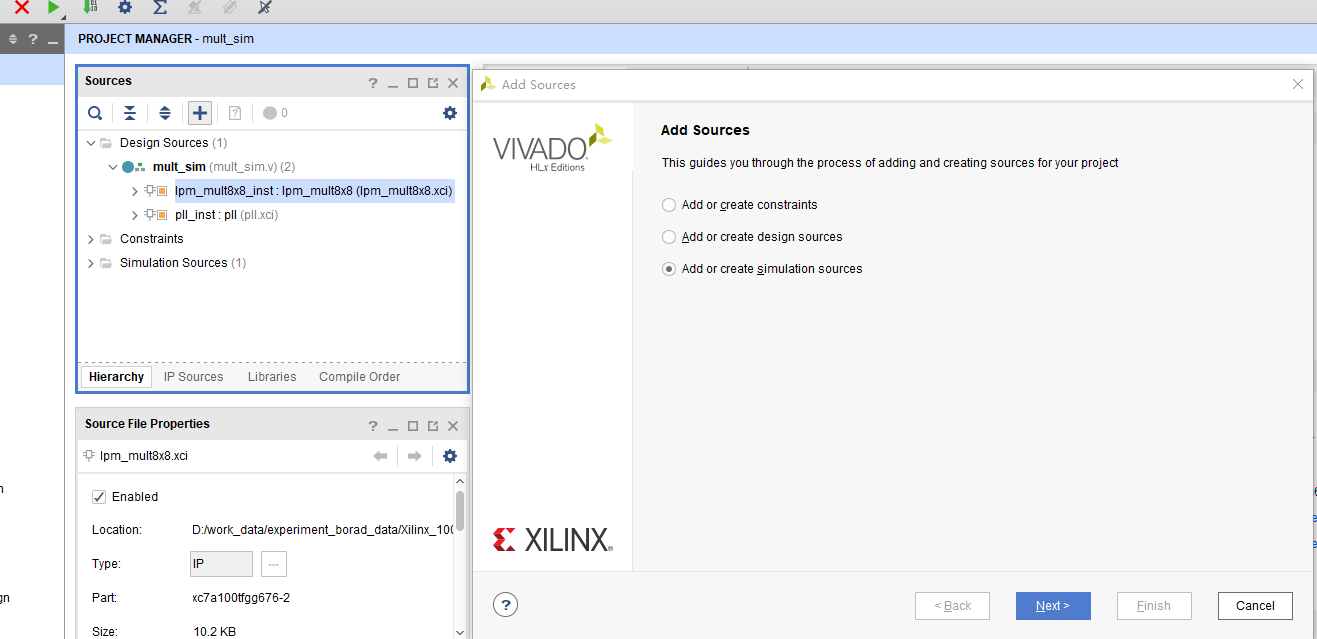

- Build simulation project files.

Add the testbench file under Simulation Sources. See Fig 7. 4.

Fig 7. 4 Add the testbench file

Simulation testbench code is as follows:

| module mult_sim_tb;

//Define simulation signals reg rst_n; reg [7:0] sw; reg clk; wire [7:0] seven_seg; wire [3:0] scan; wire [15:0] mult_res; wire [7: 0] count ; mult_sim mult_sim_inst ( .rst_n(rst_n), .inclk(clk), .sw(sw), .count(count), .mult_res(mult_res), .seven_seg(seven_seg), .scan(scan) ); initial begin rst_n=0; clk = 1; sw = 0; #5 rst_n=1; #15 sw = 20; #20 sw = 50; #20 sw = 100; #20 sw = 101; #20 sw = 102; #20 sw = 103; #20 sw = 104; #50 sw = 105; $monitor(“%d * %d=%d”, count, sw, mult_res); #1000000 $stop; end always #10 clk=~clk; endmodule |

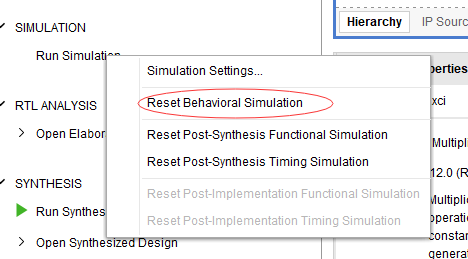

- As shown in Fig 7. 5, after the simulation stimulus file is added, ISIM can be started in Simulation->Run Simulation –> Run Behavioral Simulation on the left side of the project management.

Fig 7. 5 Simulation library compiled

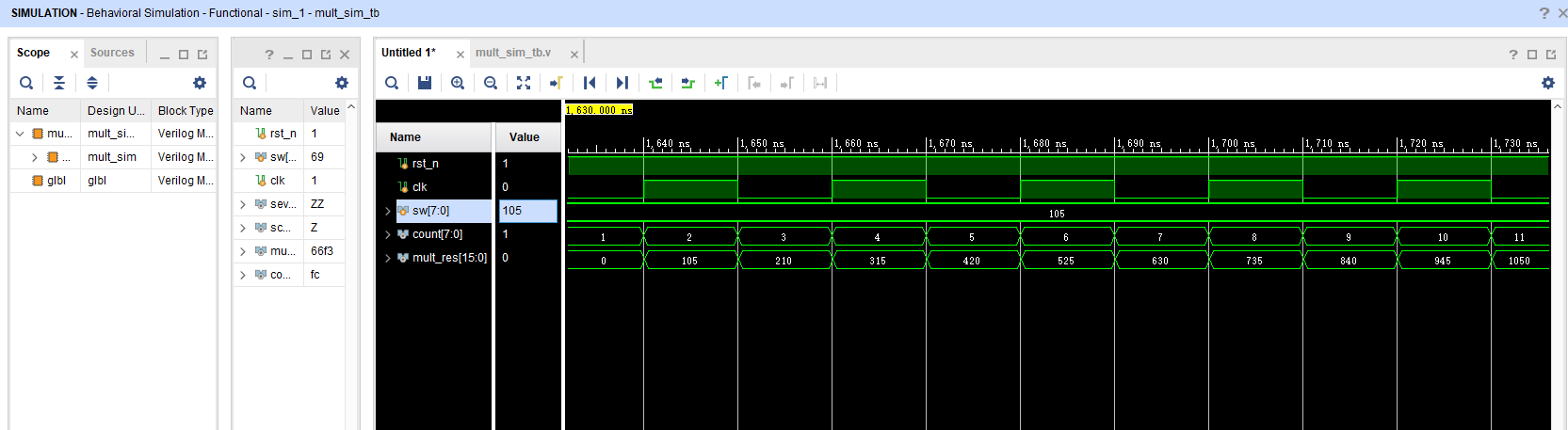

- Simulation result is shown in Fig 7. 6.

Fig 7. 6 Simulation result

- Compile ModelSim library

After installing ModelSim, compile the Xilinx simulation library file first. The specific process is as follows:

-

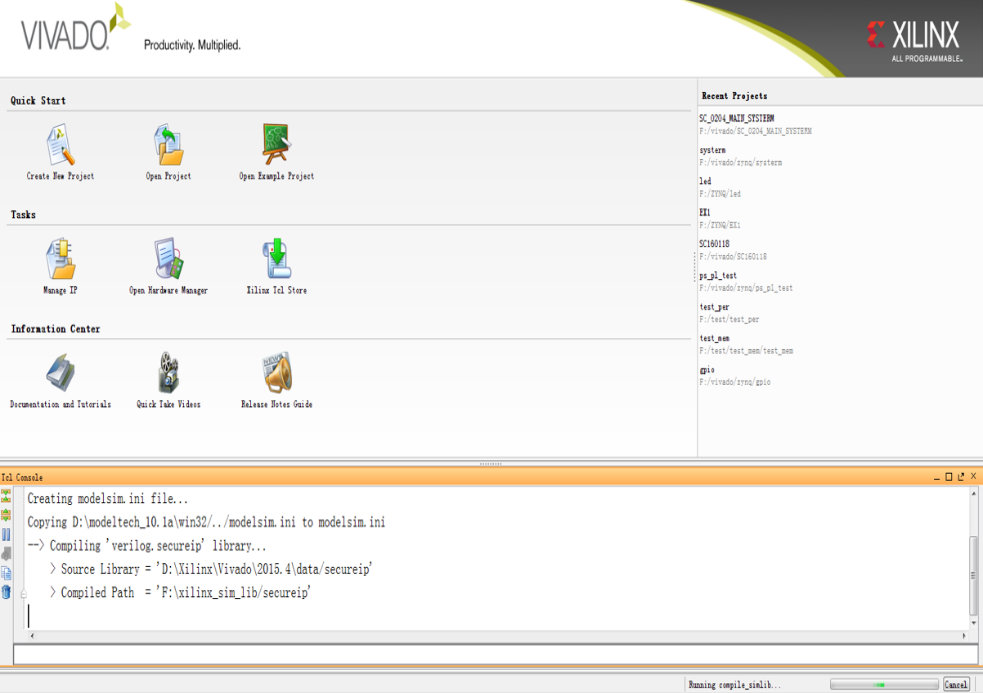

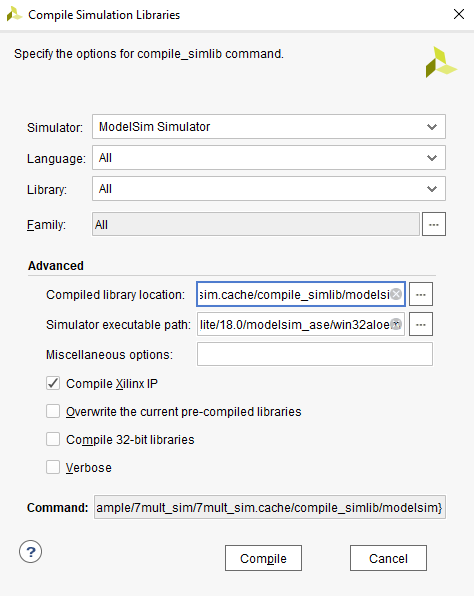

-

- Tools -> Compile Simulation Libraries. See Fig 7. 7 for the popup window.

-

Fig 7. 7 Compilation library address setting

-

-

- As shown in Fig 7. 8, the compilation is completed. Note that the process is very time consuming.

-

Fig 7. 8 Simulation library compiled

Approachable advanced information for ModelSim can be referred online. Here would not go into more details.

- More to practice

- Design an 8-bit trigger, simulate with Modelsim

- Learn to write testbenchs for simulation

Experiment 8 Hexadecimal Number to BCD Code Conversion and Application

1.Experiment Objective

-

- Since the hexadecimal display is not intuitive, decimal display is more widely used in real life.

- Human eye recognition is relatively slow, so the display from hexadecimal to decimal does not need to be too fast. Generally, there are two methods

- Countdown method: Under the control of the synchronous clock, the hexadecimal number is decremented by 1 until it is reduced to 0. At the same time, the appropriate BCD code decimal counter is designed to increment. When the hexadecimal number is reduced to 0, the BCD counter just gets with the same value to display.

- Bitwise operations (specifically, shift bits and plus 3 here). The implementation is as follows:

- Set the maximum decimal value of the expression. Suppose you want to convert the 16-digit binary value (4-digit hexadecimal) to decimal. The maximum value can be expressed as 65535. First define five four-digit binary units: ten thousand, thousand, hundred, ten, and one to accommodate calculation results

- Shift the hexadecimal number by one to the left, and put the removed part into the defined variable, and judge whether the units of ten thousand, thousand, hundred, ten, and one are greater than or equal to 5, and if so, add the corresponding bit to 3 until the 16-bit shift is completed, and the corresponding result is obtained.

Note: Do not add 3 when moving to the last digit, put the operation result directly

-

-

-

- The Principle of hexadecimal number to BCD number conversion

-

-

Suppose ABCD is a 4-digit binary number (possibly ones, 10 or 100 bits, etc.), adjusts it to BCD code. Since the entire calculation is implemented in successive shifts, ABCDE is obtained after shifting one bit (E is from low displacement and its value is either 0 or 1). At this time, it should be judged whether the value is greater than or equal to 10. If so, the value is increased by 6 to adjust it to within 10, and the carry is shifted to the upper 4-bit BCD code. Here, the pre-movement adjustment is used to first determine whether ABCD is greater than or equal to 5 (half of 10), and if it is greater than 5, add 3 (half of 6) and then shift.

For example, ABCD = 0110 (decimal 6)

- After shifting it becomes 1100 (12), greater than 1001 (decimal 9)

- By plus 0110 (decimal 6), ABCD = 0010, carry position is 1, the result is expressed as decimal

- Use pre-shift processing, ABCD = 0110 (6), greater than 5, plus 3

- ABCD=1001(9), shift left by one

- ABCD=0010, the shifted shift is the lowest bit of the high four-bit BCD.

- Since the shifted bit is 1, ABCD = 0010(2), the result is also 12 in decimal

- The two results are the same

- Firstly, make a judgement, and then add 3 and shift. If there are multiple BCD codes at the same time, then multiple BCD numbers all must first determine whether need to add 2 and then shift.

- The first way is relatively easy. Here, the second method is mainly introduced.

Example 1:

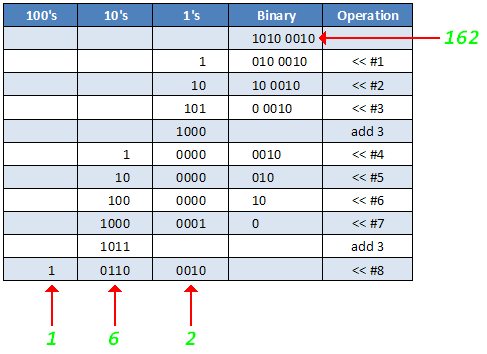

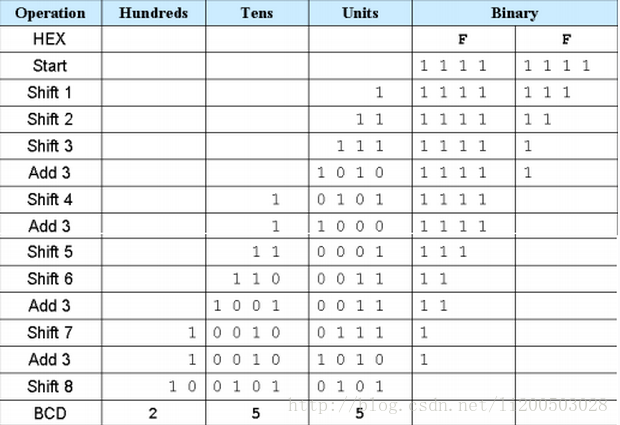

Fig 8. 1 Binary to decimal

Example 2:

Fig 8. 2 Hex to BCD

-

- Write a Verilog HDL to convert 16-bit binary to BCD. (You can find reference in the project folder, HEX_BCD.v

| `timescale 10ns/1ns

module HEX_BCD ( input [15:0] hex, output reg[3:0] ones=0, output reg[3:0] tens=0, output reg[3:0] hundreds=0, output reg[3:0] thousands=0, output reg[3:0] ten_thousands=0 ); reg [15:0] hex_reg; integer i; always@(*) begin hex_reg =hex; ones =0; tens =0; hundreds =0; thousands =0; ten_thousands=0;

for (i=15;i>=0;i=i-1)begin if(ten_thousands>=5) ten_thousands=ten_thousands+3;

if(thousands>=5) thousands=thousands+3;

if(hundreds>=5) hundreds=hundreds+3;

if(tens>=5) tens=tens+3;

if(ones>=5) ones=ones+3;

ten_thousands =ten_thousands<< 1;//Left shift operation ten_thousands[0]=thousands[3]; thousands =thousands<<1; thousands[0]=hundreds[3]; hundreds=hundreds<<1; hundreds[0]=tens[3]; tens=tens<<1; tens[0]=ones[3]; ones=ones<<1; ones[0]=hex_reg[15]; hex_reg={hex_reg[14:0],1’b0}; end end endmodule |

-

- Modelsim simulation

- Refer to last experiment for setting Modelsim

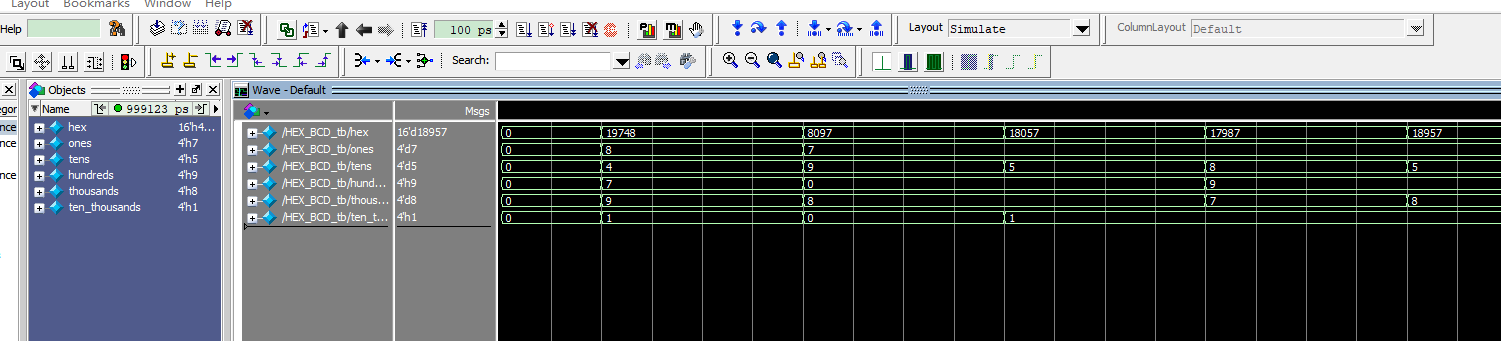

- Simulation result shown in Fig 8. 3.

- Modelsim simulation

Fig 8. 3 Simulation result for Hex to BCD

-

- Remark

The assignment marks for the examples above are “=” instead of “<=”. Why?

Since the whole program is designed to be combinational logic, when invoking the modules, the other modules should be synchronized the timing.

2.Application of Hexadecimal Number to BCD Number Conversion

- Continue to complete the multiplier of experiment 7 and display the result in segment decoders in decimal. The code is as follows:

| module mult_sim(

input rst, input inclk, input [7:0] sw, output reg[6:0] seven_sega, output reg[5:0] scan ); wire [15:0] mult_res; wire sys_clk; wire sys_rst; wire us_f; wire ms_f; wire s_f; reg [7:0] count; reg [3:0] counta; reg [6:0] seven_seg_ra; wire [3:0] ones; wire [3:0] tens; wire [3:0] hundreds; wire [3:0] thousands; wire [3:0] ten_thousands; reg [3:0] ones_r; reg [3:0] tens_r; reg [3:0] hundreds_r; reg [3:0] thousands_r; reg [3:0] ten_thousands_r; always@(posedge sys_clk) if(sys_rst) begin count <=0; ones_r <=0; tens_r <=0; hundreds_r<=0; thousands_r<=0; ten_thousands_r<=0; end else if(s_f) begin count<=count+1; ones_r <=ones; tens_r <=tens; hundreds_r<=hundreds; thousands_r<=thousands; ten_thousands_r<=ten_thousands; end reg ext_rst; always@(posedge sys_clk) ext_rst<=rst; reg [2:0] scan_st;

always@(posedge sys_clk) if(!ext_rst) begin scan<=6’b11_1111; counta<=4’b0; scan_st<=0; end else case(scan_st) 0:begin scan<=6’b11_1110; counta<=ones_r; if(ms_f) scan_st<=1; end 1:begin scan<=6’b11_1101; counta<=tens_r; if(ms_f) scan_st<=2; end 2:begin scan<=6’b11_1011; counta<=hundreds_r; if(ms_f) scan_st<=3; end 3:begin scan<=6’b11_0111; counta<=thousands_r; if(ms_f) scan_st<=4; end 4:begin scan<=6’b10_1111; counta<=ten_thousands_r; if(ms_f) scan_st<=5; end 5:begin scan<=6’b01_1111; counta<=0; if(ms_f) scan_st<=0; end default:scan_st<=0; endcase

always@(*) case(counta) 0:seven_seg_ra<=7’b100_0000; 1:seven_seg_ra<=7’b111_1001; 2:seven_seg_ra<=7’b010_0100; 3:seven_seg_ra<=7’b011_0000; 4:seven_seg_ra<=7’b001_1001; 5:seven_seg_ra<=7’b001_0010; 6:seven_seg_ra<=7’b000_0010; 7:seven_seg_ra<=7’b111_1000; 8:seven_seg_ra<=7’b000_0000; 9:seven_seg_ra<=7’b001_0000; default:seven_seg_ra<=7’b100_0000; endcase always@(posedge sys_clk) seven_sega<=seven_seg_ra;

lpm_mult8x8 lpm_mult8x8_inst ( .CLK(inclk), // input wire CLK .A(sw), // input wire [7 : 0] A .B(count), // input wire [7 : 0] B .P(mult_res) // output wire [15 : 0] P ); pll_sys_rst pll_sys_rst_inst ( .clk_in (inclk), .sys_clk (sys_clk), .sys_rst (sys_rst), .BCD_clk ( ) ); us_ms_s_div us_ms_s_div_inst ( .sys_rst (sys_rst), .sys_clk (sys_clk), .us_f (us_f), .ms_f (ms_f), .s_f (s_f) ); HEX_BCD HEX_BCD_inst ( .hex (mult_res), .ones (ones), .tens (tens), .hundreds (hundreds), .thousands (thousands), .ten_thousands (ten_thousands) ); endmodule |

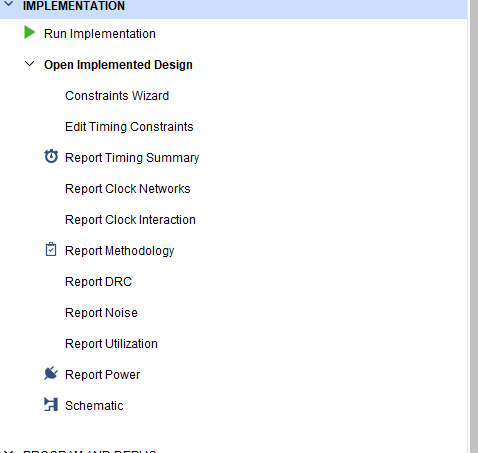

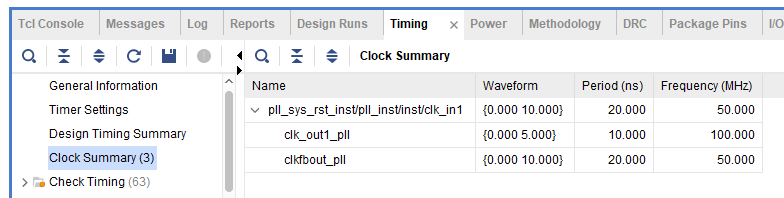

- After completing the implementation process, click Open Implementation Design as shown in Fig 8. 4. Observe the Report Timing Summary and view the circuit timing report.

Fig 8. 4 Timing report check

The result is shown in Fig 8. 5.

Fig 8. 5 Timing report

It satisfies the timing requirement.

- Pin assignment

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk | System clock, 50 MHz | C10_50MCLK | U22 |

| rst | Reset, high by default | KEY1 | M4 |

| seven_sega[0] | Segment a | SEG_PA | K26 |

| seven_sega[1] | Segment b | SEG_PB | M20 |

| seven_sega[2] | Segment c | SEG_PC | L20 |

| seven_sega[3] | Segment d | SEG_PD | N21 |

| seven_sega[4] | Segment e | SEG_PE | N22 |

| seven_sega[5] | Segment f | SEG_PF | P21 |

| seven_sega[6] | Segment g | SEG_PG | P23 |

| seven_sega[7] | Segment h | SEG_DP | P24 |

| scan[0] | Segment 6 | SEG_3V3_D5 | T24 |

| scan[1] | Segment 5 | SEG_3V3_D4 | R25 |

| scan[2] | Segment 4 | SEG_3V3_D3 | K25 |

| scan[3] | Segment 3 | SEG_3V3_D2 | N18 |

| scan[4] | Segment 2 | SEG_3V3_D1 | R17 |

| scan[5] | Segment 1 | SEG_3V3_D0 | R16 |

| sw[0] | Swicth input | GPIO_DIP_SW0 | N8 |

| sw[1] | Swicth input | GPIO_DIP_SW1 | M5 |

| sw[2] | Swicth input | GPIO_DIP_SW2 | P4 |

| sw[3] | Swicth input | GPIO_DIP_SW3 | N4 |

| sw[4] | Swicth input | GPIO_DIP_SW4 | U6 |

| sw[5] | Swicth input | GPIO_DIP_SW5 | U5 |

| sw[6] | Swicth input | GPIO_DIP_SW6 | R8 |

| sw[7] | Swicth input | GPIO_DIP_SW7 | P8 |

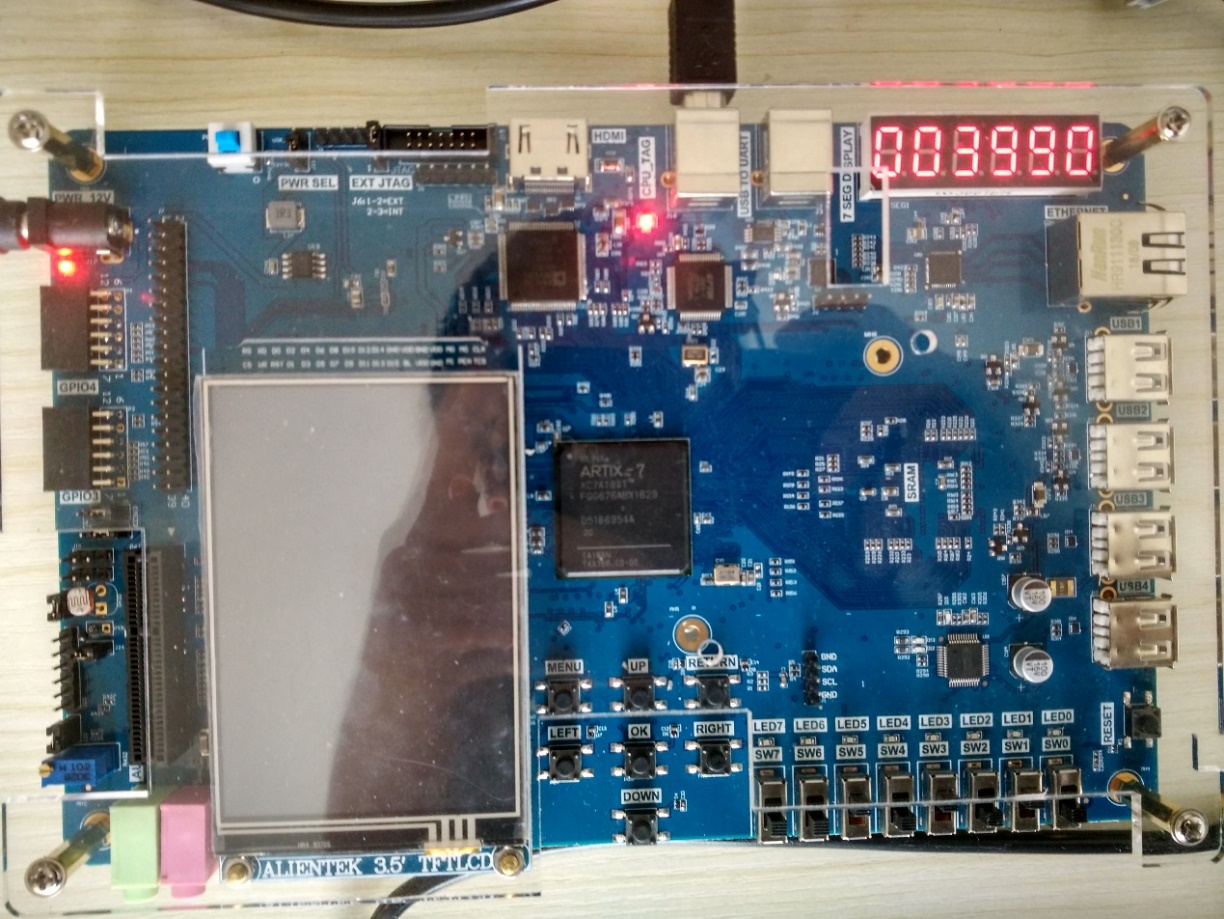

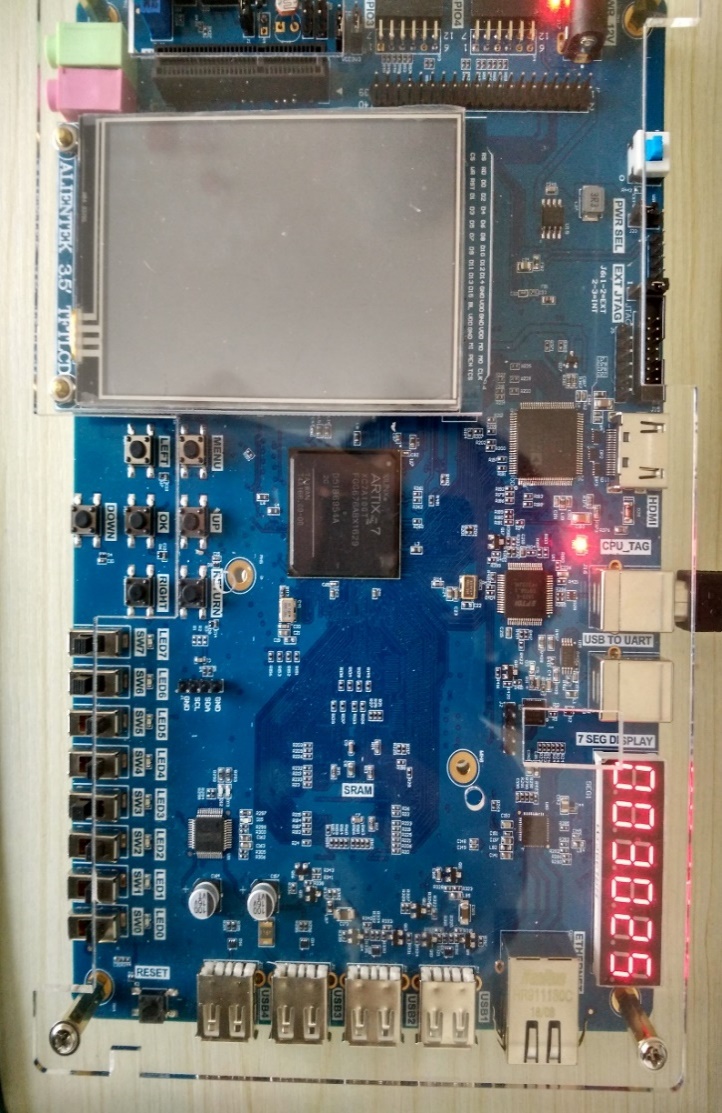

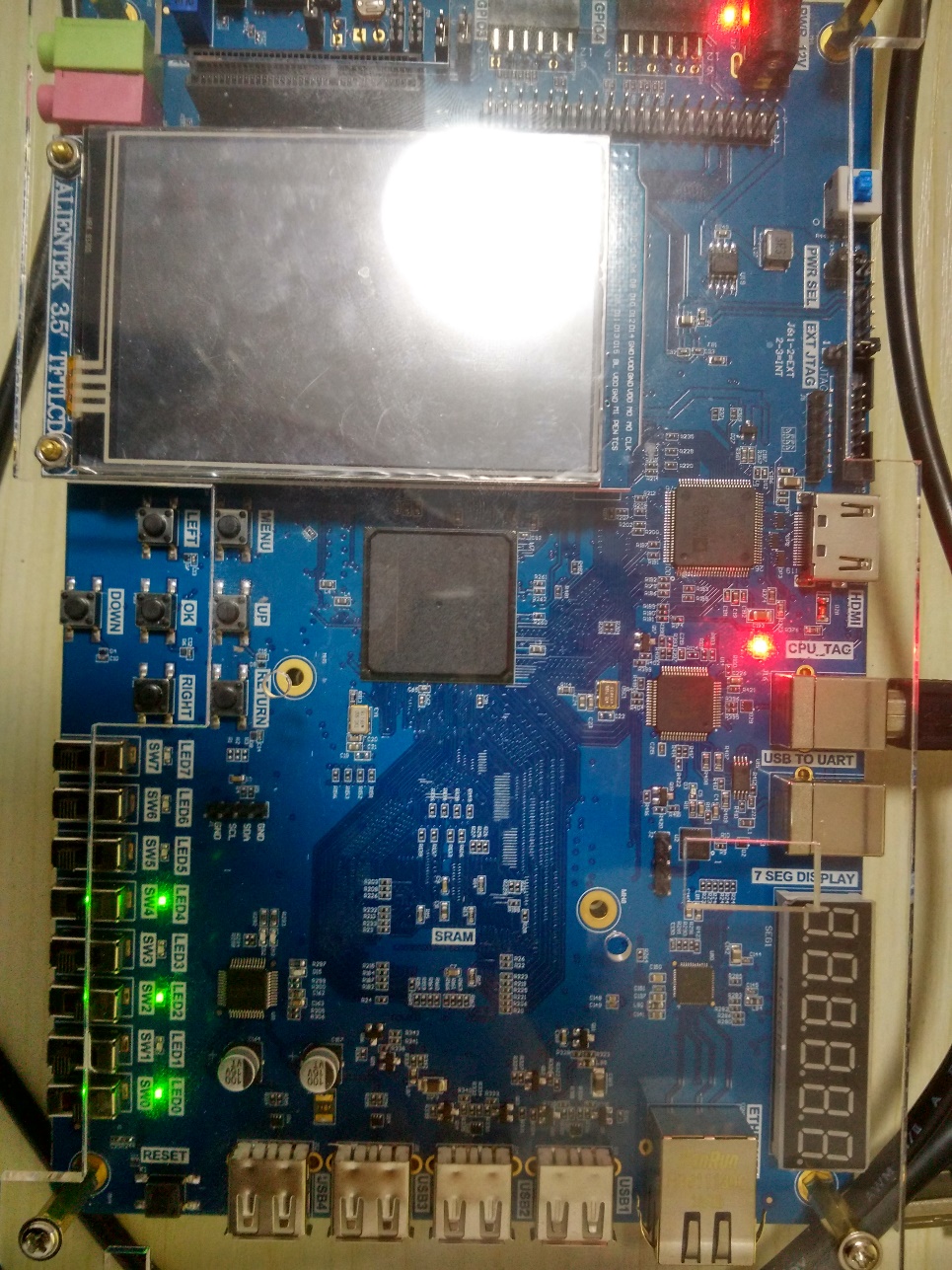

- Compile, and download the program to the board. The test result is shown below:

Fig 8. 6 Hex to BCD result

3.Experiment Reflection

-

- How to implement BCD using more than 16 bits binary numbers

- How to handle an asynchronous clock

- Learn how to design circuits that meet timing requirements based on actual needs

Experiment 9 Use of ROM

1.Experiment Objective

- Study the internal memory block of FPGA

- Study the format of *.mif and how to edit *.mif file to configure the contents of ROM

- Learn to use RAM, read and write RAM

2.Experiment Design

-

- Design 16 outputs ROM, address ranging 0-255

- Interface 8-bit switch input as ROM’s address

- Segment decoders display the contents of ROM and require conversion of hexadecimal to BCD output.

3.Design Procedure

- Create a coe file. This experiment *.coe file is generated based on Matlab2018. The *.m file is as follows:

| % –by Fraser Innovation Inc–

% function : create .coe clear all; close all; clc; depth= 256; width =16; fid_s = fopen(‘test_rom.coe’, ‘w+’); fprintf(fid_s, ‘MEMORY_INITIALIZATION_RADIX = %d;\n’,width); fprintf(fid_s, ‘%s\n’, ‘MEMORY_INITIALIZATION_VECTOR =’); for i=0:depth–1 data =i*i; b=dec2hex(data); fprintf(fid_s, ‘%s’, b); fprintf(fid_s, ‘%s\n’, ‘,’); end fclose(fid_s); disp(‘=======mif file completed========’); |

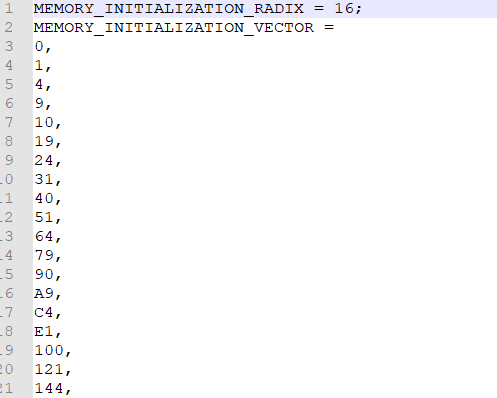

- *.coe file syntax is shown in Fig 9. 1.

Fig 9. 1 *.coe file syntax

- Create new project, rom_test, select device XC7A100TFGG676-2

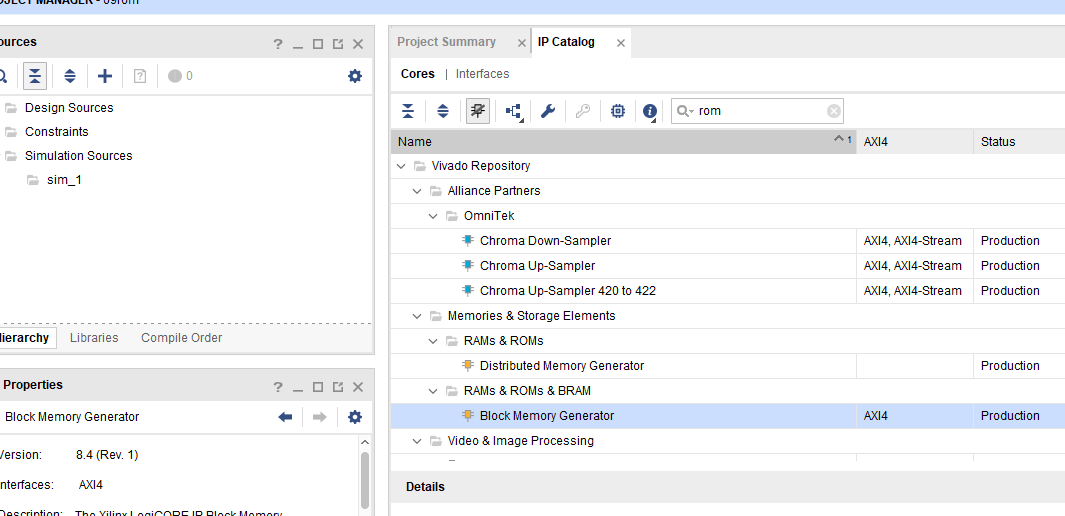

- Click IP Catalog, and input ROM in the search box. Choose Block Memory Generator. See Fig 9. 2.

Fig 9. 2 Use of ROM IP core

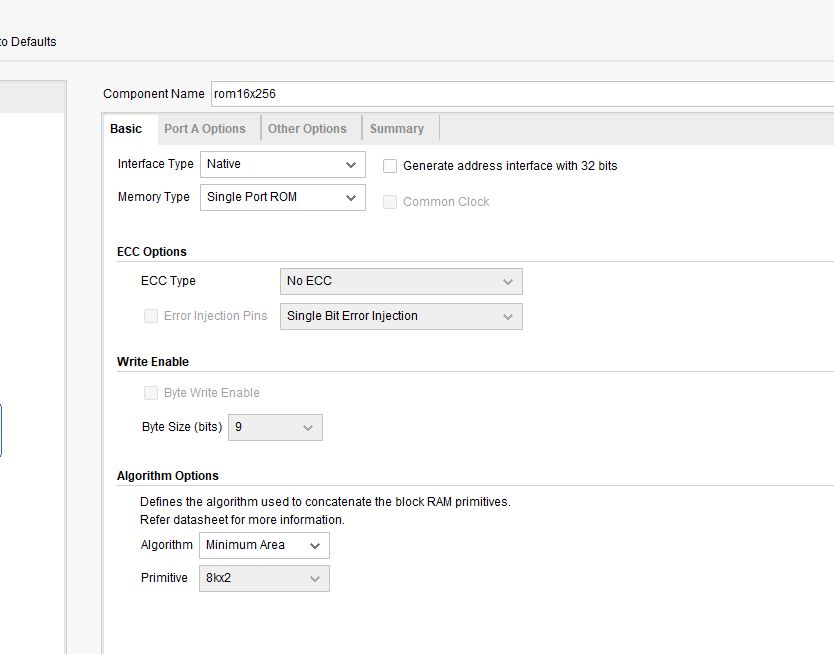

- Select the memory type be Single Port ROM. See Fig 9. 3.

Fig 9. 3 Memory type selection

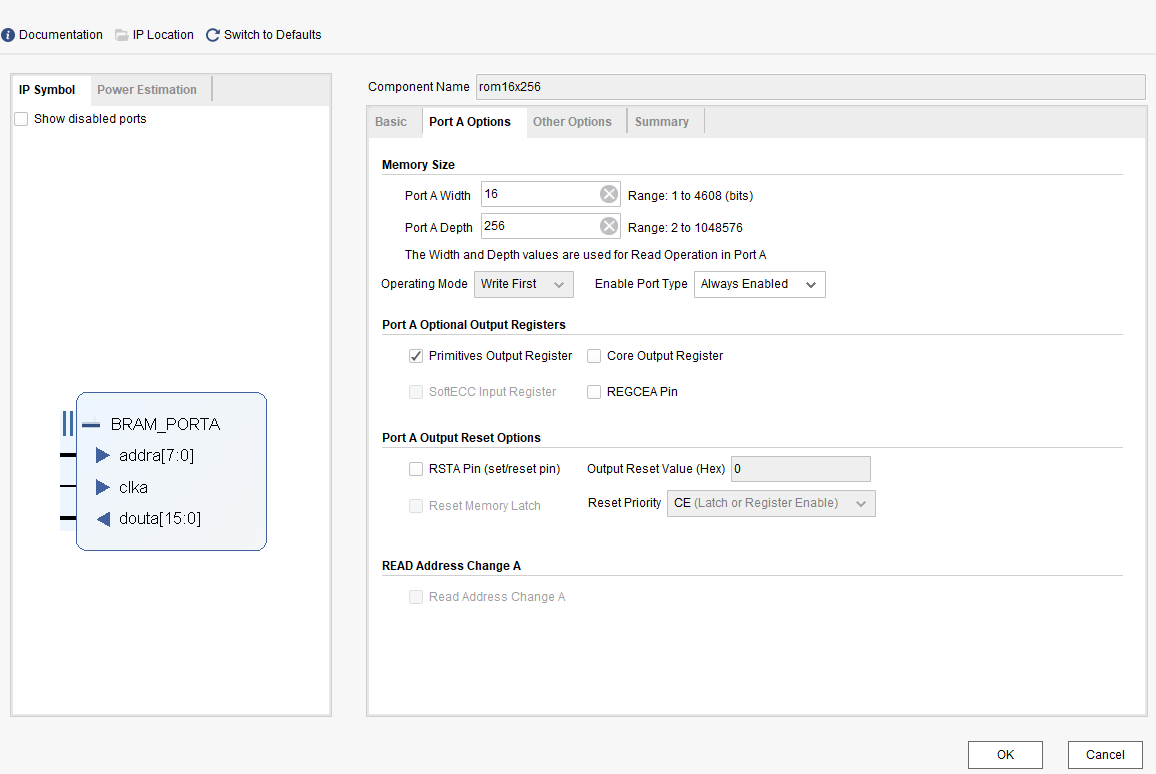

- Click Port A Options tag. Set as shown in Fig 9. 4.

Fig 9. 4 Port memory width setting

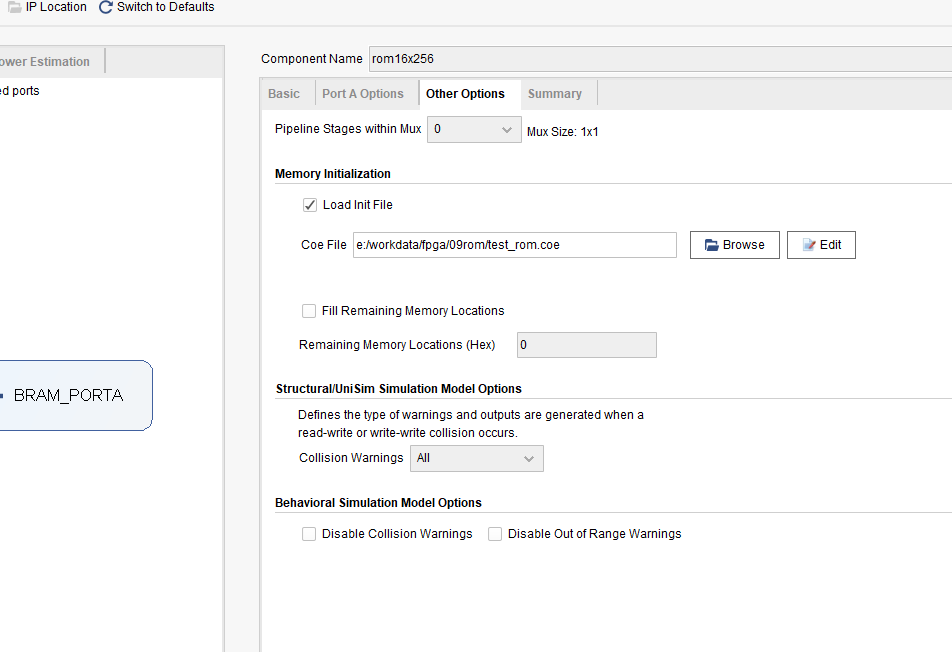

- Click the Other Options tab shown in Fig 9. 5, select the Load Init File check box, set the correct *.coe file location, and initialize the rom.

Fig 9. 5 ROM initialization

- Set others as default

- Click OK to finish setting for IP core. Generate other files related as default setting.

- Create top-level entity, rom_test.v

- Add PLL (Input clock 50 MHz, output clock 100 MHz)

- Add us_ms_s_div.v and instantiate it. Refer previous experiments for more

- Add HEX_BCD and instantiate it

- The code is given below:

| module rom_test(

input rst, input inclk, input [7:0] sw, output reg[5:0] scan, output reg[6:0] seven_sega );

wire [15:0] rom_q; wire sys_clk; wire BD_clk; wire sys_rst; wire u_f; wire m_f; wire sf; reg [7:0] count; reg [5:0] counta; reg [6:0] seven_seg_ra;

wire [3:0] ones; wire [3:0] tens; wire [3:0] hundreds; wire [3:0] thousands; wire [3:0] ten_thousands;

reg [3:0] ones_r; reg [3:0] tens_r; reg [3:0] hundreds_r; reg [3:0] thousands_r; reg [3:0] ten_thousands_r;

reg [3:0] ones_x; reg [3:0] tens_x; reg [3:0] hundreds_x; reg [3:0] thousands_x; reg [3:0] ten_thousands_x; always@(posedge BCD_clk) begin ones_x <= ones; tens_x <= tens; hundreds_x <= hundreds; thousands_x <= thousands; ten_thousands_x <= ten_thousands; end always@(posedge sys_clk) if(sys_rst) begin count <= 0; ones_r <= 0; tens_r <= 0; hundreds_r <= 0; thousands_r <= 0; ten_thousands_r <= 0; end else if(s_f) begin count <= count+1; ones_r <= ones_x; tens_r <= tens_x; hundreds_r <= hundreds_x; thousands_r <= thousands_x; ten_thousands_r <= ten_thousands_x; end

reg ext_rst; always@(posedge sys_clk) ext_rst<=rst; reg [2:0] scan_st;

always@(posedge sys_clk) if(!ext_rst) begin scan<=6’b11_1111; counta<=4’b0;

scan_st<=0; end

else case(scan_st)

0 : begin scan <= 6’b11_1110; counta <= ones_r; if( ms_f ) scan_st <= 1; end

1 : begin scan <=6’b11_1101; counta <=tens_r; if ( ms_f ) scan_st<=2; end

2 : begin scan <=6’b11_1011; counta <=hundreds_r; if(ms_f) scan_st<=3; end

3 : begin scan <=6’b11_0111; counta <=thousands_r; if(ms_f) scan_st<=4; end

4 : begin scan <=6’b10_1111; counta <=ten_thousands_r; if(ms_f) scan_st<=5; end

5 : begin scan <=6’b01_1111; counta <=0; if (ms_f) scan_st<=0; end

default:scan_st<=0; endcase always@(*) case(counta) 0 : seven_sega <= 7’b100_0000 ; 1 : seven_sega <= 7’b111_1001 ; 2 : seven_sega <= 7’b010_0100 ; 3 : seven_sega <= 7’b011_0000 ; 4 : seven_sega <= 7’b001_1001 ; 5 : seven_sega <= 7’b001_0010 ; 6 : seven_sega <= 7’b000_0010 ; 7 : seven_sega <= 7’b111_1000 ; 8 : seven_sega <= 7’b000_0000 ; 9 : seven_sega <= 7’b001_0000 ; default: seven_sega<=7’b100_0000 ; endcase

pll_sys_rst pll_sys_rst_inst( .clk_in(inclk), .sys_clk(sys_clk), .BCD_clk(BCD_clk), .sys_rst(sys_rst) );

us_ms_s_div us_ms_s_div_inst ( .sys_rst(sys_rst), .sys_clk(sys_clk), .us_f (us_f), .ms_f (ms_f), .s_f (s_f) );

reg [15:0] rom_q_r; always@(posedge BCD_clk) rom_q_r<=rom_q; HEX_BCD HEX_BCD_inst( .hex (rom_q_r), .ones (ones), .tens (tens), .hundreds (hundreds), .thousands (thousands), .ten_thousands (ten_thousands) );

rom16x256 rom16x256_inst ( .clka(sys_clk), // input wire clka .addra(sw), // input wire [7 : 0] addra .douta(rom_q) // output wire [15 : 0] douta );

endmodule |

-

- Compile

- Lock the pins

| Signal Name | Port Description | Network Label | FPGA Pin |

| inclk | Sytem clock, 50 MHz | C10_50MCLK | U22 |

| rst | Reset, hight by default | KEY1 | M4 |

| seven_sega[0] | Segment a | SEG_PA | K26 |

| seven_sega[1] | Segment b | SEG_PB | M20 |

| seven_sega[2] | Segment c | SEG_PC | L20 |

| seven_sega[3] | Segment d | SEG_PD | N21 |

| seven_sega[4] | Segment e | SEG_PE | N22 |

| seven_sega[5] | Segment f | SEG_PF | P21 |

| seven_sega[6] | Segment g | SEG_PG | P23 |

| seven_sega[7] | Segment h | SEG_DP | P24 |

| scan[0] | Segment 6 | SEG_3V3_D5 | T24 |

| scan[1] | Segment 5 | SEG_3V3_D4 | R25 |

| scan[2] | Segment 4 | SEG_3V3_D3 | K25 |

| scan[3] | Segment 3 | SEG_3V3_D2 | N18 |

| scan[4] | Segment 2 | SEG_3V3_D1 | R17 |

| scan[5] | Segment 1 | SEG_3V3_D0 | R1 6 |

| sw[0] | Switch input | GPIO_DIP_SW0 | N8 |

| sw[1] | Switch input | GPIO_DIP_SW1 | M5 |

| sw[2] | Switch input | GPIO_DIP_SW2 | P4 |

| sw[3] | Switch input | GPIO_DIP_SW3 | N4 |

| sw[4] | Switch input | GPIO_DIP_SW4 | U6 |

| sw[5] | Switch input | GPIO_DIP_SW5 | U5 |

| sw[6] | Switch input | GPIO_DIP_SW6 | R8 |

| sw[7] | Switch input | GPIO_DIP_SW7 | P8 |

-

- Download the program and test the result

Fig 9. 6 Test result

- Experiment summary and reflection

- How to use the initial file of ROM to realize the decoding, such as decoding and scanning the segment decoders.

- Write a *.mif file to generate sine, cosine wave, and other function generators.

- Comprehend application, combine the characteristic of ROM and PWM to form SPWM modulation waveform.

Experiment 10 Use Dual_port RAM to Read and Write Frame Data

1.Experiment Objective

-

- Learn to configure and use dual-port RAM

- Learn to use synchronous clock to control the synchronization of frame structure

- Learn to use asynchronous clock to control the synchronization of frame structure

- Observing the synchronization structure of synchronous clock frames using ILA

- Extended the use of dual-port RAM

- Design the use of three-stage state machine

2.Experiment Implement

- Generate dual-port RAM and PLL

- 16-bit width, 256-depth dual-port RAM

- 2 PLL, both 50 MHz input, different 100 MHz and 20 MHz outputs

- Design a 16-bit data frame

- Data is generated by an 8-bit counter: Data={~counta,counta}

- The ID of the data frame inputted by the switch (7 bits express maximum of 128 different data frames)

- 16-bit checksum provides data verification

-

-

- 16-bit checksum accumulates, discarding the carry bit

- After the checksum is complemented, append to the frame data

-

-

- Provide configurable data length data_len by parameter

- Packet: When the data and checksum package are written to the dual-port RAM, the userID, the frame length and the valid flag are written to the specific location of the dual-port RAM. The structure of the memory is shown below

| Wr_addr | Date/ Flag | Rd_addr |

| 8’hff | {valid, ID, data_len} | 8’hff |

| … | N/A | … |

| 8’hnn+2 | N/A | 8’hnn+2 |

| 8’hnn+1 | ~checksum+1 | 8’hnn+1 |

| 8’hnn | datann | 8’hnn |

| … | …. | … |

| 8’h01 | Data1 | 8’h01 |

| 8’h00 | Data0 | 8’h00 |

- Read and write in an agreed order

Firstly, write in the order

- Read the flag of the 8’hff address (control word). If valid=1’b0, the program proceeds to the next step, otherwise waits

- Address plus 1, 8’hff+1 is exactly zero, write data from 0 address and calculate the checksum

- Determine whether the interpretation reaches the predetermined data length. If so, proceeds to next step, otherwise the data is written, and the checksum is calculated.

- checksum complements and write to memory

- Write the control word in the address 8’hff, packet it

Secondly, read in the order

- Idle is the state after reset

- Init: Initialization, set the address to 8’hff

- Rd_pipe0: Add a latency (since the read address and data are both latched). Address +1, forming a pipeline structure

- Read0: Set the address to 8’hff, read the control word and judge whether the valid bit is valid.

If valid=1’b1, address +1, proceeds to the next step

If valid=1’b0, it means the packet is not ready yet, the address is set to be 8’hff and returns to the init state.

- Read1: Read the control word again

If valid=1’b1, address+1, ID and data length are assigned to the corresponding variables and proceeds to the next step

If valid=1’b0, it means the packet is not ready yet, the address is set to 8’hff, and returns to the init state.

- Rd_data:

Read data and pass to data variables

Calculate checksum, data_len – 1

Determine whether the data_len is 0, if so, all data has been read, proceeds to the next step, otherwise, continue the operation in current state

- grd_chsum: Read the value of checksum and calculate the last checksum. Correct the data and set the flag of rd_err

- rd_done: The last step clears the valid flag in memory and opens the write enable for the next packet.

Thirdly, valid is the handshake signal. This flag provides the possibility of read and write synchronization, so the accuracy of this signal must be ensured in the program design. See the project files for more details.

3.Program Design

-

- Port

module frame_ram

#(parameter data_len=250)

(

input inclk,

input rst, //external reset

input [6:0] sw, //used as input ID

output reg[6:0] oID, //used as output ID

output reg rd_done, //frame read is done

output reg rd_err //frame read has errors

);

-

- Definition of state machine

parameter [2:0] mema_idle=0,

mema_init=1,

mema_pipe0=2,

mema_read0=3,

mema_read1=4,

mema_wr_data=5,

mema_wr_chsum=6,

mema_wr_done=7;

parameter [2:0] memb_idle=0,

memb_init=1,

memb_pipe0=2,

memb_read0=3,

memb_read1=4,

memb_rd_data=5,

memb_rd_chsum=6,

memb_rd_done=7;

-

- Define clock parameter

wire sys_clk;

wire BCD_clk;

wire sys_rst;

reg ext_clk;

-

- Define two-port RAM interface

reg [7:0] addr_a;

reg [15:0] data_a;

reg wren_a;

wire [15:0] q_a;

reg [7:0] addr_b;

reg wren_b;

wire [15:0] q_b;

-

- Write state machine partial variable definition

- Write stste machine variables

- Write state machine partial variable definition

reg[6:0] user_id;

reg[7:0] wr_len;

reg[15:0] wr_chsum;

Wire wr_done;

reg[7:0] counta;

Wire[7:0] countb=~counta;

Reg ext_rst;

Reg [2:0] sta;

reg[2:0] sta_nxt;

-

-

- Read state machine variables

-

reg[15:0] rd_chsum;

reg[7:0] rd_len;

reg[15:0] rd_data;

Reg ext_rst;

reg[2:0] stb;

reg[2:0] stb_nxt;

-

- Data generation counter

always@(posedge BCD_clk)

ext_rst<=rst;

always@(posedge sys_clk)

if(sys_rst) begin

counta <=0;

user_id <=0;

end

else begin

counta <=counta+1;

user_id<=sw;

End

-

- Write state machine

- First and second stages

- Write state machine

assign wr_done=(wr_len==data_len-1);//Think why using wr_len==data_len-1

//instead of wr_len==data_len

always@(posedge sys_clk)

if(sys_rst) begin

sta=mema_idle;

end

else

sta=sta_nxt;

always@(*)

case (sta)

mema_idle : sta_nxt=mema_init;

mema_init : sta_nxt=mema_pipe0;

mema_pipe0 : sta_nxt=mema_read0;

mema_read0 :begin

if(!q_a[15])

sta_nxt=mema_read1;

else

sta_nxt=sta;

end

mema_read1:begin

if(!q_a[15])

sta_nxt=mema_wr_data;

else

sta_nxt=sta;

end

mema_wr_data: begin

if(wr_done)

sta_nxt=mema_wr_chsum;

else

sta_nxt=sta;

end

mema_wr_chsum: sta_nxt=mema_wr_done;

mema_wr_done: sta_nxt=mema_init;

default:sta_nxt=mema_idle;

endcase

-

-

- Third stage

-

always@(posedge sys_clk)

case (sta)

mema_idle: begin

addr_a<=8’hff;

wren_a<=1’b0;

data_a<=16’b0;

wr_len<=8’b0;

wr_chsum<=0;

end

mema_init,mema_pipe0,mema_read0,mema_read1: begin

addr_a<=8’hff;

wren_a<=1’b0;

data_a<=16’b0;

wr_len<=8’b0;

wr_chsum<=0;

end

mema_wr_data:begin

addr_a<=addr_a+1;

wren_a<=1’b1;

data_a<={countb,counta};

wr_len<=wr_len+1;

wr_chsum<=wr_chsum+{countb,counta};

end

mema_wr_chsum:begin

addr_a<=addr_a+1;

wr_len<=wr_len+1;

wren_a<=1’b1;

data_a<=(~wr_chsum)+1’b1;

end

mema_wr_done:begin

addr_a<=8’hff;

wren_a<=1’b1;

data_a<={1’b1,user_id,wr_len};

end

default:;

endcase

-

- Read state machine

- First stage

- Read state machine

always@(posedge sys_clk)

if(!ext_rst) begin

stb=memb_idle;

end

else

stb=stb_nxt;

-

-

- Second stage

-

always@(*)

case (stb)

memb_idle : stb_nxt=memb_init;

memb_init : stb_nxt=memb_pipe0;

memb_pipe0 : stb_nxt=memb_read0;

memb_read0 :begin

if(q_b[15])

stb_nxt=memb_read1;

else

stb_nxt=memb_init;

end

memb_read1:begin

if(q_b[15])

stb_nxt=memb_rd_data;

else

stb_nxt=memb_init;

end

memb_rd_data: begin

if(rd_done)

stb_nxt=memb_rd_chsum;

else

stb_nxt=stb;

end

memb_rd_chsum: stb_nxt=memb_rd_done;

memb_rd_done: stb_nxt=memb_init;

default:stb_nxt=memb_idle;

endcase

-

-

- Third stage. The actual operation is driven by the edge of the clock

-

always@(posedge sys_clk)

case(stb)

memb_idle: begin

addr_b<=8’hff;

rd_data<=0;

rd_chsum<=0;

wren_b<=1’b0;

rd_len<=8’b0;

oID<=7’b0;

rd_err<=1’b0;

end

memb_init: begin

addr_b<=8’hff;

rd_data<=0;

rd_chsum<=0;

wren_b<=1’b0;

rd_len<=8’b0;

oID<=7’b0;

rd_err<=1’b0;

endmemb_pipe0: begin

addr_b<=8’b0;

end

memb_read0: begin

if(q_b[15])

addr_b<=addr_b+1’b1;

else

addr_b<=8’hff;

rd_data<=0;

rd_chsum<=0;

wren_b<=1’b0;

rd_len<=8’b0;

oID<=7’b0;

end

memb_read1: begin

if(q_b[15])

addr_b<=addr_b+1’b1;

else

addr_b<=8’hff;

rd_data<=0;

rd_chsum<=0;

wren_b<=1’b0;

rd_len<=q_b[7:0];

oID<=q_b[14:8];

end

memb_rd_data: begin

addr_b<=addr_b+1’b1;

rd_data<=q_b;

rd_chsum<=rd_chsum+rd_data;

wren_b<=1’b0;

rd_len<=rd_len-1’b1;

end

memb_rd_chsum: begin

addr_b<=8’hff;

wren_b<=1’b0;

if(!rd_chsum)//Determine if rd_chsum is not 0, else error occurs when reading data

rd_err<=1’b1;

end

memb_rd_done: begin

addr_b<=8’hff;

wren_b<=1’b1;

end

default:;

endcase

always@(*)begin

if(stb==memb_rd_data)

rd_done=(rd_len==0);

else

rd_done=1’b0;

end

-

- Instantiate dual_port RAM and PLL

//Instantiate dual-port RAM

dp_ram dp_ram_inst

(

.address_a(addr_a),

.address_b(addr_b),

.clock (sys_clk),

.data_a (data_a),

.data_b (16’b0),

.wren_a (wren_a),

.wren_b(wren_b),

.q_a (q_a),

.q_b (q_b)

);

//Instantiate PLL

pll_sys_rst pll_sys_rst_inst

(

.inclk (inclk),

.sys_clk (sys_clk),

.BCD_clk(BCD_clk),

.sys_rst (sys_rst)

);

endmodule

4.Lock the Pins, Compile, and Download to The Board to Test

- Pin assignment

| Signal Name | Port Description | Network Label | FPGA Pin |

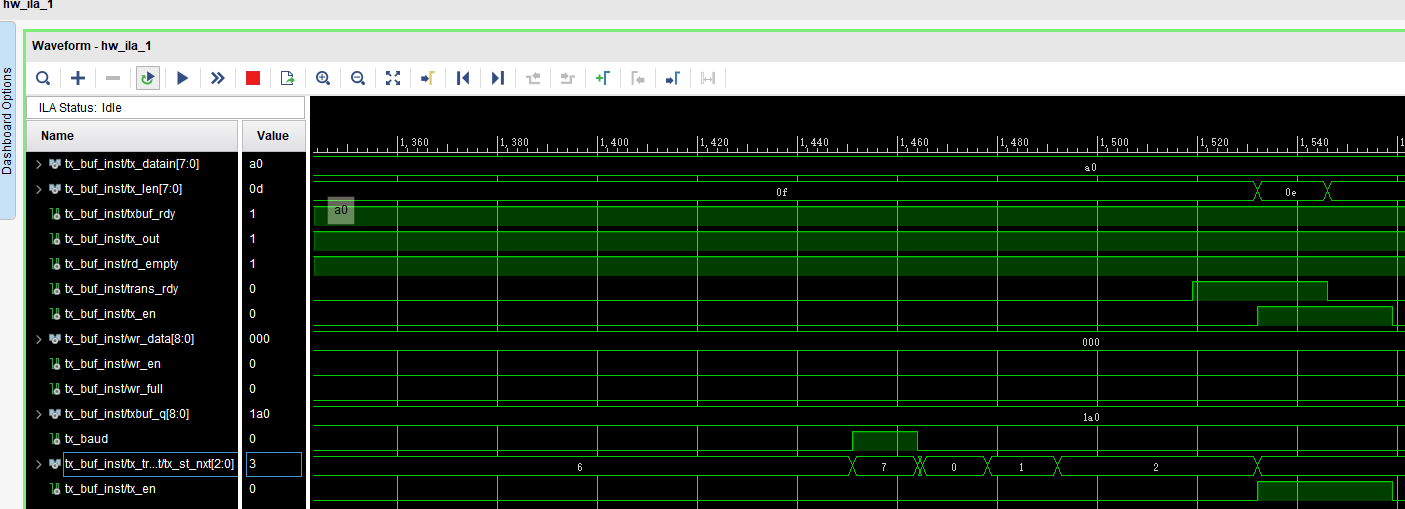

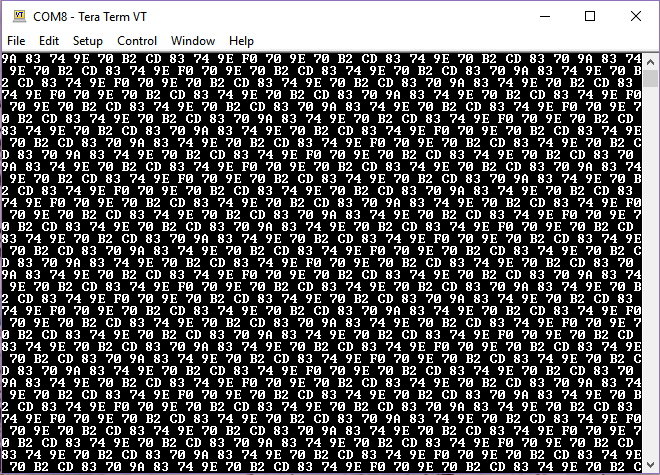

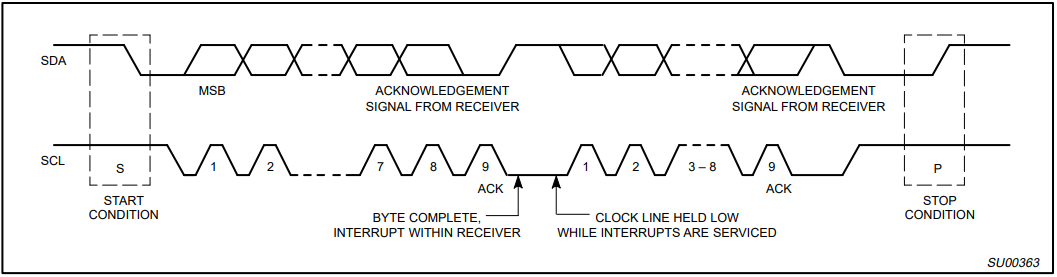

| inclk | System clock, 50 MHz | C10_50MCLK | U22 |